MC8051 IP核基本结构及原理

2013-05-26

1 MC8051功能特点

采用完全同步设计:指令集和标准8051微控制器完全兼容;指令执行时间为l~4个时钟周期,执行性能优于标准805l微控制器8倍左右;用户可选择定时/计数器、串行接口单元的数量,最多可增加到256组;新增特殊功能寄存器用于选择不同的定时/计数器、串行接口单元;可选择是否使用乘法器(乘法指令MUL);可选择是否使用除法器(除法指令DIV);可选择是否使用十进制调整功能(十进制调整指令DA);I/0口不复用,无双向数据I/O端口,输入、输出端口独立;内部带256Byte RAM;⑾最多可扩展至64 KB的ROM和64 KB的RAM;与工艺无关,可通过修改VHDL源代码扩展及参数化设置。

2 MC8051结构及设计层次

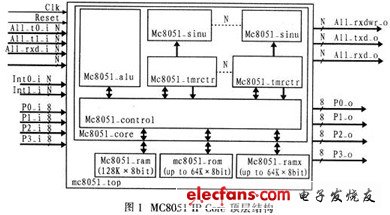

图1给出MC805l_eore的顶层设计模块及其子模块,包括顶层的各个信号端口及3个存储器模块。同时给出了顶层的输入输出I/O口。定时/计数器和串行接口单元,对应于图中的MC805l_tmrctr和MC8051_siu模块,数量可选择,图中用虚线表示。MC8051 IP核与工业标准8051单片机不同,MC8051的输入、输出并口分别映射到独立的端口上。其顶层各I/O信号的描述如表l所示。

MC805lIP核的设计层次及对应的VHDL文件如图2所示嘲。它由定时/计数器、ALU算数逻辑单元、串行接口单元和控制单元组成。RAM及ROM模块不包括在IP核内,处于设计的顶层,方便于不同的应用设计及仿真。

图2中,最顶层是用户的实际应用设计模块,它将ROM、RAM及mc8051_core封装在内部。实际应用中用户可添加自定义附加逻辑模块,与设计层次中的RAM、ROM模块处于同一个层次。

下一篇:解析100G传输方案及应用

- 将ASIC IP核移植到FPGA上——如何测试IP核的功能和考虑纯电路以外的其他因素

- 将ASIC IP核移植到FPGA上——如何确保性能与时序以完成充满挑战的任务!

- 将ASIC IP核移植到FPGA上——更新概念并推动改变以完成充满挑战的任务!

- 数字芯片设计验证经验分享:将ASIC IP核移植到FPGA上——需求和详细规划以完成充满挑任务

- 更深入了解汽车与航空电子等安全关键型应用的IP核考量因素

- 基于OC8051IP核的仿真调试方案在FPGA中实现下载测试

- 在嵌入FPGA的IP核8051微处理器上实现UIP协议栈的设计方法

- 基于APEX20K和ARM7 TDMI-S微处理器实现通用智能传感器IP核的设计

- SiFive推出媲美x86与Cortex-A78的IP核

- Achronix Speedcore eFPGA IP核出货量超千万

- 国产高精度、高速率ADC芯片,正在崛起

- 贸泽开售用于快速开发精密数据采集系统的 Analog Devices ADAQ7767-1 μModule DAQ解决方案

- 采用电容型PGA,纳芯微推出高精密多通道24/16位Δ-Σ型ADC

- ADALM2000实验:变压器

- 意法半导体推出灵活、节省空间的车载音频 D类放大器,新增针对汽车应用优化的诊断功能

- 安森美CEO亮相慕尼黑Electronica展,推出Treo平台

- 全差分放大器为精密数据采集信号链提供高压低噪声信号

- 安森美推出业界领先的模拟和混合信号平台

- 集Hi-Fi、智能和USB多通道等特征于一体的微控制器——迎接数字音频新时代

- 高信噪比MEMS麦克风驱动人工智能交互