高介电常数栅电介质/金属栅极的FA CMP技术

2013-05-27

典型的RMG工艺流程依次包括(图1):临时多晶硅栅极结构的形成,第一层间电介质(ILD0)氧化硅的沉积,ILD0化学机械研磨直至临时多晶硅栅极完全曝露,刻蚀去除多晶硅栅极,功函数材料的淀积,金属铝的沉积,以及金属铝的化学机械研磨。作为RMG工艺流程步骤之一,ILD0化学机械研磨对于HKMG结构的顺利形成至关重要。

由于栅极结构对尺寸控制要求非常严格(WIW和WID),如果缺少严格控制最终研磨厚度的工艺手段,将会带来一系列的工艺整合问题,比如:栅极电阻波动,栅极填充不足,源/漏极曝露等等。这些问题最终都会损害芯片性能。为了确保芯片的优良性能和可靠性,制造工艺必须严格控制WIW、WID以及WTW的厚度差异。

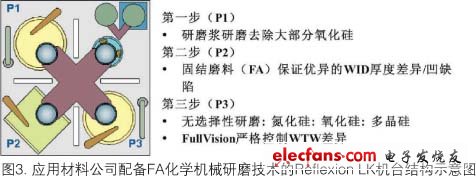

应用材料公司已经成功研发出一套在Reflexion? LK机台上实现的三步化学机械研磨工艺,以解决ILD0化学机械研磨过程中的WIW、WID和WTW厚度控制问题。第一步(P1),研磨移除大部分的ILD0电介质材料;第二步(P2),采用FA继续研磨,接触到栅极区域氮化硅层后停止;第三步(P3),栅极区域的氮化硅层被彻底磨掉,多晶硅栅极完全曝露。图2演示了在ILD0化学机械研磨过程中,沟槽区氧化硅研磨去除的全过程。

实验细节

应用材料公司的Reflexion? LK研磨机台包括一个FA研磨盘和两个标准的旋转式研磨浆研磨盘,使用可以控制5个独立区域压力的Titan ContourTM研磨头(图3)。FA研磨盘配有3M公司生产的SlurryFreeTM 固结磨料卷轴和SlurryFree P6900基底研磨垫。研磨浆研磨盘配有Dow Chemical公司生产的IC1010TM研磨垫和3M公司生产的研磨垫修复刷。P1使用Cabot公司生产的Semi-SperseR SS-12氧化硅研磨浆;P2使用FA研磨液;P3使用专用的研磨浆。

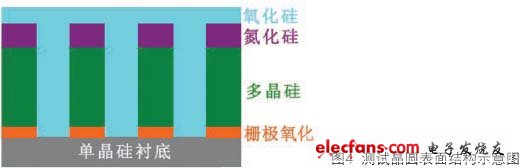

本文将统一使用一种简化的栅极结构(图4)以评估不同工艺的表现。栅极区域结构从上到下依次为:氧化硅/氮化硅/多晶硅/栅极氧化物/单晶硅,“沟槽”特指栅极与栅极之间的区域(结构为:氧化硅/单晶硅)。在尺寸大于50微米的测量区,薄膜厚度的测量使用Nanometrics公司的NanoTM 9010b。而对栅极尺寸小于100纳米的测量点,则需要通过扫描电子显微镜(SEM)进行纵切面观测。本文中,一部分样品通过机械劈裂的方式获得晶圆纵切面;另一部分样品使用聚焦离子束(FIB)局部切割晶圆露出纵切面。

结果与讨论

P3需要无选择性的研磨浆

因为P3之后的平坦度要求非常严格,P3的研磨倾向于使用无选择性研磨浆。该研磨浆在氮化硅、氧化硅和多晶硅上都有可观的磨率。首先,氮化硅的磨率必需足够高才能保证多晶硅栅极完全曝露。如果氧化硅的研磨率显著低于氮化硅和多晶硅,则可能导致沟槽区域明显凸起,并随着过度研磨而恶化。如果多晶硅的研磨率显著低于氮化硅和氧化硅,那么栅极和沟槽之间的高度差会对研磨不足或过度研磨非常敏感。使用无选择性的研磨浆将会减少由于P3研磨时间不同造成的栅极和沟槽之间的高度差变化。

P2 FA工艺可以降低P3之后沟槽氧化硅的WID厚度差异

FA工艺已被广泛应用于直接研磨浅沟槽隔离(STI)。FA可以选择性的停在氮化硅表面,并展现出优异的研磨平坦度和低的凹缺陷。与STI类似,ILD0的研磨也包括停在氮化硅表面的步骤。这种极低氮化硅损失和极低氧化硅凹缺陷的工艺特点使得FA成为ILD0研磨工艺中WIW和WID厚度控制的关键。在栅极密集区,由于特征尺寸很小,不论使用FA工艺还是高选择性的研磨浆(HSS)研磨工艺,凹缺陷一般都比较低(图5)。然而在外围区域,特征尺寸可能达到50微米以上,HSS研磨工艺一般都会产生明显的凹缺陷(>200?),而FA研磨工艺仍能保持低凹缺陷(<50?)。

因此,对比FA工艺和HSS工艺研磨后的沟槽氧化硅WID厚度差异,前者明显低于后者。由于P3使用无选择性的研磨浆,P2之后的高凹缺陷就会直接导致P3之后的沟槽氧化硅WID厚度差异也很高(图5)。从晶圆纵切面的SEM照片中可以清楚的看出P3之后的WID厚度差异。

FA优异的平坦度和凹缺陷表现

与HSS工艺相比,FA工艺能够明显降低沟槽氧化硅的WID厚度差异和凹缺陷,尤其在大特征尺寸区域。与此同时,FA过度研磨不会显著降低WIW和WID表现(图7)。图6对比了FA和HSS工艺在不同特征尺寸下的凹缺陷表现。当特征尺寸达到50微米时,凹缺陷的表现就会有明显差异。FA优异的凹缺陷表现使其成为RMG ILD0化学机械研磨工艺的关键步骤。

P2对于P3工艺的影响

图8-11中,所有SEM照片的拍摄角度均为45度。晶圆纵切面通过FIB切割方式获得。所有的照片使用相同的比例尺。图8比较了P2用HSS工艺研磨后的栅极密集区和200×200微米测量点的沟槽氧化硅厚度。栅极密集区和大尺寸测量区的厚度明显不同,表明存在显著的WID差异。P3的无选择性研磨浆工艺将很难修复P2造成的WID差异。如图9所示,如果P2使用HSS工艺,栅极密集区和大尺寸测量区的沟槽氧化硅厚度差异在P3之后仍然会很高。

相对于HSS,FA研磨后的WID厚度差很小。图10显示沟槽氧化硅在密集区和大尺寸测量区的厚度非常接近。这种低WID差异会被进一步保留至无选择性的P3之后(图11)。上述对比显示,FA有能力解决线路密度和尺寸不同造成的平坦度挑战,从而减少芯片设计规则中对于线路密度的限制。

用FullVision控制多晶硅厚度

持续稳定的多晶硅厚度控制是通过FullVision实时终点控制系统来实现的。该系统的可靠性和可重复性已在实际生产中得到证明。图12显示出FullVision终点控制系统的强大功能。在图12中,晶圆A和B都使用标准P3工艺研磨,并利用FullVision控制研磨终点;晶圆C和D的P3磨率低于标准磨率10%;晶圆C通过FullVision控制研磨终点,而晶圆D的研磨时间与晶圆A和B的研磨时间相同。上述四片晶圆的P1和P2研磨条件完全相同。

FullVision自动调整晶圆C的研磨时间来补偿P3磨率的下降。因此,晶圆A、B和C在P3之后的栅极多晶硅厚度差异小于5?。由于晶圆D没有使用FullVision终点侦测控制系统,而是使用与晶圆A相同的研磨时间进行研磨,因此晶圆D在P3之后的栅极多晶硅厚度与标准工艺条件的平均厚度相差高达25?。

使用无选择性的P3研磨浆会使工艺本身对P3磨率随研磨垫寿命的偏移以及上游步骤工艺的变化(比如氮化硅厚度改变,P2过度研磨程度等)非常敏感。FullVision可以通过自动调节研磨时间来应对生产过程中各种无法预测的偏移,从而确保稳定的WTW表现。

无论是在栅极密集区还是在大尺寸测量区,图13中的SEM纵切面图片都展示出均一的表面形貌。

结论

良好的WID、WIW和WTW厚度控制是制造基于HKMG技术的高性能逻辑芯片的关键。ILD0化学机械研磨工艺利用FA对不同尺寸大小和密度的芯片结构均提供优异的表面形貌和平坦度控制,并且通过使用FullVision实时终点控制系统进一步确保稳定的WTW厚度控制。

- 国产高精度、高速率ADC芯片,正在崛起

- 贸泽开售用于快速开发精密数据采集系统的 Analog Devices ADAQ7767-1 μModule DAQ解决方案

- 采用电容型PGA,纳芯微推出高精密多通道24/16位Δ-Σ型ADC

- ADALM2000实验:变压器

- 意法半导体推出灵活、节省空间的车载音频 D类放大器,新增针对汽车应用优化的诊断功能

- 安森美CEO亮相慕尼黑Electronica展,推出Treo平台

- 全差分放大器为精密数据采集信号链提供高压低噪声信号

- 安森美推出业界领先的模拟和混合信号平台

- 集Hi-Fi、智能和USB多通道等特征于一体的微控制器——迎接数字音频新时代

- 高信噪比MEMS麦克风驱动人工智能交互