如何在RF电路中选择LDO稳压器的PSRR和输出噪声

2010-11-24

LDO是一种微功耗的低压差线性稳压器,它具有极低的自有噪声和较高的电源抑制比(PSRR)。SGM2007高性能低压差线性稳压器在10Hz至100kHz频率范围内的输出噪声为30 μV(RMS),在 1 kHz 的频率下电源抑制比(PSRR)高达73dB,它能够为诸如射频(RF)接收器和发送器、压控振荡器(VCO)和音频放大器等对噪声敏感的模拟电路的供电提供低噪声、电源纹波抑制比(PSRR)和快速瞬态响应,它的使能电路兼容TTL电平适合数字电路供电。SGM2007的输入电压在2.5V至5.5V之间,适合蓝牙数码相机和个人数字助理(PDA),以及诸如无线和高端音频产品等单个锂电池供电或固定3.3V和5V系统。

LDO的低压差线性稳压器的结构主要包括启动电路、恒流源偏置单元、使能电路、调整元件、基准源、误差放大器、反馈电阻网络,保护电路等,基本工作原理是这样的:系统加电,如果使能脚处于高电平时,电路开始启动,恒流源电路给整个电路提供偏置,基准源电压快速建立,输出随着输入不断上升,当输出即将达到规定值时,由反馈网络得到的输出反馈电压也接近于基准电压值,此时误差放大器将输出反馈电压和基准电压之间的误差小信号进行放大,再经调整管放大到输出,从而形成负反馈,保证了输出电压稳定在规定值上;同理如果输入电压变化或输出电流变化,这个闭环回路将使输出电压保持不变,即:

Vout=(R1+R2)/R2 * Vref

Power supply ripple rejection ratio (PSRR)是反应LDO输出对输入纹波抑制的一个交流参数,输出和输入的频率是一样的。和噪声(Nosie)不同,噪声一般为在10Hz至100kHz频率范围内一定输入电压下其输出噪声电压的均方值,PSRR的单位是dB。

PSRR=20 log(△vin/△vout)

大多数蜂窝电话基带芯片组需要三组电源:内部数字电路、模拟电路和外设接口电路。基带处理器(BB)的数字电路供电电压的典型值为1.8V至2.6V,一般情况下,Li+电池电压降至3.2V-3.3V时电话将被关闭,对于为基带处理器供电的LDO来说至少有500至600mV的压差,因此对压差要求不高。另外,数字电路本身对LDO的输出噪声和PSRR的要求也不高,而是要求LDO在轻载条件下具有极低的静态电流。

基带处理器内部模拟电路供电电压典型值是2.4V至3.0V,压差在200mV至600mV。要求LDO具有较高的低频(GSM电话为217Hz)纹波抑制能力,消除由RF功率放大器产生的电池电压纹波。LDO始终保持有效工作状态,同样需要较低的静态电流指标。

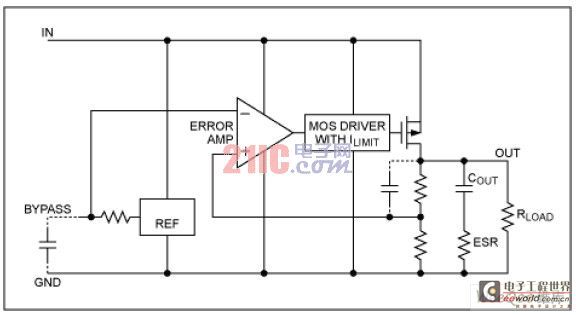

RF电路分为接收和发送两部分,供电电压典型值为2.6V至3.0V,其中低噪声放大器(LNA)、混频器、锁相环(PLL)、压控振荡器(VCO)和中频(IF)电路需要低噪声、高PSRR的LDO。实际应用中,VCO、PLL电路的性能直接影响射频电路指标,如发射频谱的纯度、接收器的选择性、模拟收发器的噪声、数字电路的相位误差等。噪声会改变振荡器的相频和幅频特性,同时振荡器环路也会进一步放大噪声,可能对载波产生调制。LDO输出噪声受其内部设计和外部旁路、补偿电路的影响。如图是线性稳压器的简单框图。导致LDO输出噪声的主要来源是基准。

为降低基准噪声,用于连接基准旁路电容。增大旁路电容能够使基准噪声成为产生LDO输出噪声的次要因素,有利于减小输出噪声。建议使用陶瓷电容的典型值为 470 pF 到 0.01 μF 。也可使用此范围以外的电容,但会对输入电源上电时LDO 输出电压上升的速度产生影响,旁路电容值越大,输出电压上升速率越慢。在使用时这点要注意。

影响LDO输出噪声的其它因素还有:LDO内部极点、零点

LDO是一种微功耗的低压差线性稳压器,它具有极低的自有噪声和较高的电源抑制比(PSRR)。SGM2007高性能低压差线性稳压器在10Hz至100kHz频率范围内的输出噪声为30 μV(RMS),在 1 kHz 的频率下电源抑制比(PSRR)高达73dB,它能够为诸如射频(RF)接收器和发送器、压控振荡器(VCO)和音频放大器等对噪声敏感的模拟电路的供电提供低噪声、电源纹波抑制比(PSRR)和快速瞬态响应,它的使能电路兼容TTL电平适合数字电路供电。SGM2007的输入电压在2.5V至5.5V之间,适合蓝牙数码相机和个人数字助理(PDA),以及诸如无线和高端音频产品等单个锂电池供电或固定3.3V和5V系统。

LDO的低压差线性稳压器的结构主要包括启动电路、恒流源偏置单元、使能电路、调整元件、基准源、误差放大器、反馈电阻网络,保护电路等,基本工作原理是这样的:系统加电,如果使能脚处于高电平时,电路开始启动,恒流源电路给整个电路提供偏置,基准源电压快速建立,输出随着输入不断上升,当输出即将达到规定值时,由反馈网络得到的输出反馈电压也接近于基准电压值,此时误差放大器将输出反馈电压和基准电压之间的误差小信号进行放大,再经调整管放大到输出,从而形成负反馈,保证了输出电压稳定在规定值上;同理如果输入电压变化或输出电流变化,这个闭环回路将使输出电压保持不变,即:

Vout=(R1+R2)/R2 * Vref

Power supply ripple rejection ratio (PSRR)是反应LDO输出对输入纹波抑制的一个交流参数,输出和输入的频率是一样的。和噪声(Nosie)不同,噪声一般为在10Hz至100kHz频率范围内一定输入电压下其输出噪声电压的均方值,PSRR的单位是dB。

PSRR=20 log(△vin/△vout)

大多数蜂窝电话基带芯片组需要三组电源:内部数字电路、模拟电路和外设接口电路。基带处理器(BB)的数字电路供电电压的典型值为1.8V至2.6V,一般情况下,Li+电池电压降至3.2V-3.3V时电话将被关闭,对于为基带处理器供电的LDO来说至少有500至600mV的压差,因此对压差要求不高。另外,数字电路本身对LDO的输出噪声和PSRR的要求也不高,而是要求LDO在轻载条件下具有极低的静态电流。

基带处理器内部模拟电路供电电压典型值是2.4V至3.0V,压差在200mV至600mV。要求LDO具有较高的低频(GSM电话为217Hz)纹波抑制能力,消除由RF功率放大器产生的电池电压纹波。LDO始终保持有效工作状态,同样需要较低的静态电流指标。

RF电路分为接收和发送两部分,供电电压典型值为2.6V至3.0V,其中低噪声放大器(LNA)、混频器、锁相环(PLL)、压控振荡器(VCO)和中频(IF)电路需要低噪声、高PSRR的LDO。实际应用中,VCO、PLL电路的性能直接影响射频电路指标,如发射频谱的纯度、接收器的选择性、模拟收发器的噪声、数字电路的相位误差等。噪声会改变振荡器的相频和幅频特性,同时振荡器环路也会进一步放大噪声,可能对载波产生调制。LDO输出噪声受其内部设计和外部旁路、补偿电路的影响。如图是线性稳压器的简单框图。导致LDO输出噪声的主要来源是基准。

为降低基准噪声,用于连接基准旁路电容。增大旁路电容能够使基准噪声成为产生LDO输出噪声的次要因素,有利于减小输出噪声。建议使用陶瓷电容的典型值为 470 pF 到 0.01 μF 。也可使用此范围以外的电容,但会对输入电源上电时LDO 输出电压上升的速度产生影响,旁路电容值越大,输出电压上升速率越慢。在使用时这点要注意。

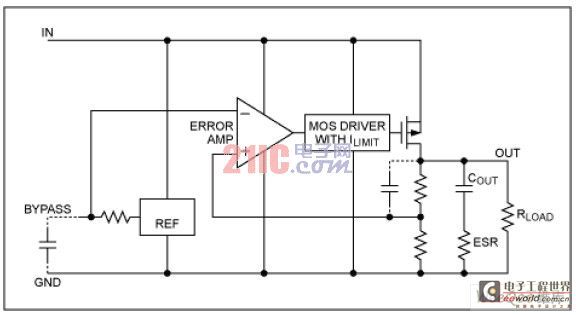

影响LDO输出噪声的其它因素还有:LDO内部极点、零点输出极点。增大输出电容的容量或减轻输出负载有利于降低高频输出噪声。如图为旁路电容对SG2001输出噪声影响。

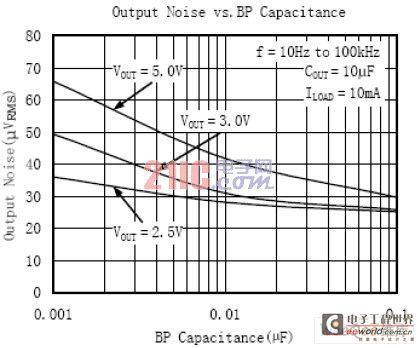

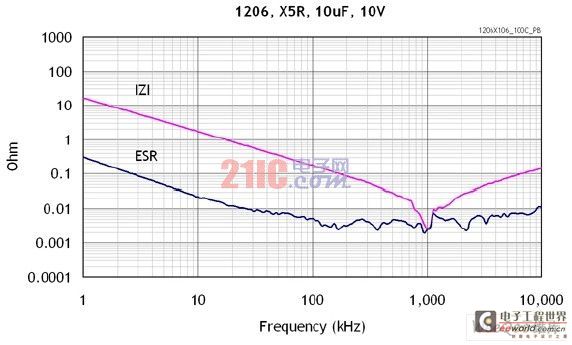

LDO需要增加外部输入和输出电容器。利用较低ESR的大电容器一般可以全面提高电源抑制比(PSRR)、噪声以及瞬态性能。 陶瓷电容器通常是首选,因为它们价格低而且故障模式是断路,相比之下钽电容器比较昂贵且其故障模式是短路。输出电容器的等效串联电阻(ESR)会影响其稳定性,陶瓷电容器具有较低的ESR,大概为10 mΩ量级 采用陶瓷电容时,建议使用X5R 和X7R电介质材料,这是因为它们具有较好的温度稳定性。图为X5R的ESR和频率曲线。

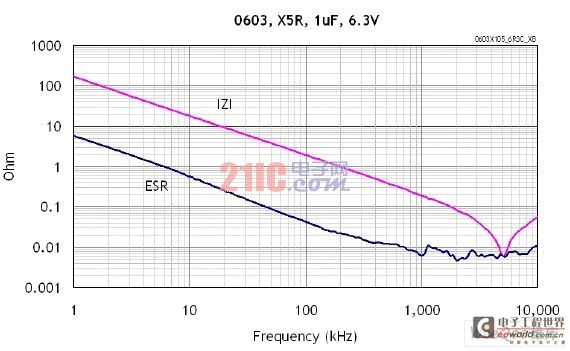

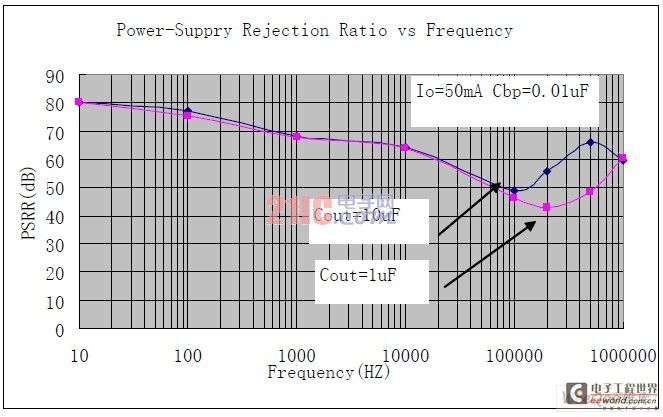

如图为输出电容对PSRR的影响。大电容器一般在一定频率范围内会提高电源抑制比(PSRR)

为射频电路选择LDO时,要慎重比较噪声指标,和电源抑制比(PSRR),确保旁路电容、输出电容和负载条件一致。新型音频电路,如免提电话、游戏机、MP3及蜂窝电话中的多媒体电路,可能需要300mA-500mA的大电流LDO,LDO要在音频范围(20Hz至20kHz)应具有低噪声、高PSRR特性,以保证良好的音质。

- 从隔离到三代半:一文看懂纳芯微的栅极驱动IC

- 华为固态电池新突破:硫化物电解质专利发布,破解液态电池衰减难题

- 48V 技术的魅力:系统级应用中的重要性、优势与关键要素

- MathWorks 和 NXP 合作推出用于电池管理系统的 Model-Based Design Toolbox

- 如何选择电压基准源

- 氮化镓取代碳化硅?PI颠覆式1700V InnoMux2先来打个样

- 废旧锂离子电池回收取得重要突破

- 面向车载应用的 DC/DC 电源

- 南芯科技推出面向储能市场的80V高效同步双向升降压充电芯片

- 强茂SGT MOSFET第一代系列:创新槽沟技术 车规级60 V N通道 突破车用电子的高效表现

- 非常见问题解答第223期:如何在没有软启动方程的情况下测量和确定软启动时序?

- Vicor高性能电源模块助力低空航空电子设备和 EVTOL的发展

- Bourns 推出两款厚膜电阻系列,具备高功率耗散能力, 采用紧凑型 TO-220 和 DPAK 封装设计

- Bourns 全新高脉冲制动电阻系列问世,展现卓越能量消散能力

- Nexperia推出新款120 V/4 A半桥栅极驱动器,进一步提高工业和汽车应用的鲁棒性和效率

- 英飞凌推出高效率、高功率密度的新一代氮化镓功率分立器件

- Vishay 新款150 V MOSFET具备业界领先的功率损耗性能

- 强茂SGT MOSFET第一代系列:创新槽沟技术 车规级60 V N通道 突破车用电子的高效表现

- 面向车载应用的 DC/DC 电源