利用单片机实现复杂的分立逻辑

2024-11-05 来源:EEWORLD

开发人员可利用PIC16F13145系列单片机中的可配置逻辑模块(CLB)外设实现硬件中复杂的分立逻辑功能,从而精简物料清单(BOM)并开发定制专用逻辑。

在许多嵌入式系统应用中,通常都会使用分立式逻辑器件,例如74'HC系列。这些逻辑器件的优势在于可以独立于单片机(MCU)工作,并且响应速度比软件快得多。但是,这些器件会增加物料清单(BOM)并且需要占用额外的PCB面积。

为了解决这一问题,Microchip的许多单片机都集成了一种名为可配置逻辑单元(CLC)的外设(在PIC® MCU上)或名为可配置定制逻辑(CCL)的类似外设(在AVR® MCU上)。这两种外设都实现了软件定义的定制逻辑,可以独立于CPU执行。换句话说,一旦设置了定制逻辑功能,其行为就独立于单片机。

但是,这两种外设存在限制,即每个实例的逻辑数量非常小。每个CLC大约相当于一个查找表(LUT),而CCL相当于一个内部具有几个独立LUT的实例。这两种外设的功能非常强大,可用于开发简单逻辑电路、将各种信号混合在一起以及与其他硬件外设相集成。例如,硬件按钮去抖、WS2812输出生成和正交解码这些示例都需要使用这两种外设,但单片机中这两种外设的数量并不多,因此限制了应用的复杂度。

为了支持更复杂的应用,PIC16F13145系列单片机引入了一种名为可配置逻辑模块(CLB)的新型逻辑外设(如图1所示)。请注意,CLB并不会取代CLC或CCL外设,器件可以同时配备CLC/CCL和CLB。

图1—— CLB框图

PIC16F13145系列单片机上的CLB包含四个逻辑组,每组包含八个BLE。不同逻辑组的BLE之间彼此连接——每个逻辑组代表两个GPIO输出和一个可选的CPU中断。当工作电压为5.5V时,BLE的传播时间典型值小于6 ns。整个结构中的所有BLE共用一个公共时钟,其时钟源与可选的时钟分频器一起在软件中进行配置。CLB可以使用单片机的内部时钟源之一或外部提供的时钟源。

该外设从单片机的存储器中进行初始化,之后可通过外设引脚选择(PPS)直接从自身结构中控制引脚。用户可通过PPS重新分配用于硬件外设的I/O引脚,从而获得更大的设计灵活性。举例来说,如果SPI时钟先前使用RA1,但使用RA6会更有利,那么便可以通过PPS重新映射引脚。

CLB中的其他元件包括专用的3位硬件定时器(带解码输出)、用于输入信号的边沿检测器以及32位输出寄存器(用于调试)。单片机上的其他独立于内核的外设(CIP)输出可用作CLB的输入,以便实现更复杂的设计。

由于CLB比CLC或CCL复杂得多,因此Microchip开发了一款名为CLB合成器的新工具。CLB合成器提供了一个用于配置逻辑的图形界面,如下面的图2所示。除了逻辑原语之外,该工具还支持更高级的逻辑模块库(可由用户预先提供或定制)。

与该图形工具交互时,后台会自动生成一个Verilog模块用于合成。如果开发人员更喜欢编写自己的Verilog或者已准备好该文件,则可以将其作为模块直接导入工具。

图2——已打开相移键控(PSK)示例的CLB合成器

CLB合成器的输出是一个汇编文件,其中包含用于设置CLB的比特流和一些用于将CLB配置为外设的源代码。该工具可通过MPLAB®代码配置器(MCC)或独立在线工具运行。MCC是一款代码生成实用程序,允许用户使用可视化界面来设置和配置单片机中的外设。当硬件外设完成配置后,MCC将生成初始化代码和器件API。

在运行时,使用板上硬件直接从程序存储器加载CLB比特流。这种实现的好处在于如果在程序运行时需要更改CLB配置,则可以使用存储在器件存储器中的不同比特流重复执行加载过程。

为了演示CLB的应用,我们创建了一系列用例示例。这里我们将讨论两个示例:7段显示转换器和SPI至WS2812转换器。用例示例可作为构件复制以用作完整解决方案的一部分。这里旨在展示该外设的实用性以及它能够为设计带来哪些价值。

第一个用例是7段显示转换器。7段显示器可通过一组普通的I/O引脚驱动,但标准实现通常需要使用软件定义的查找表将输入数字转换为适合显示器的正确输出模式。在该实现中,CLB充当硬件查找表。所需的输出字符(0到F)从软件加载到CLB输入寄存器中。显示器的每个输出段均由LUT控制,以将输入映射到输出。

该用例示例在内部用于构建计时系统的新控制板。最初的用户界面是在20世纪80年代使用74'HC系列逻辑开发。使用CLB后,一个20引脚的单片机即可实现电路板上的显示和键盘逻辑,极大地精简了物料清单(BOM)。图3并排给出了两种方案以供比较。

图3——原PCB与新PCB的并排比较。该示例由Josh Booth开发。

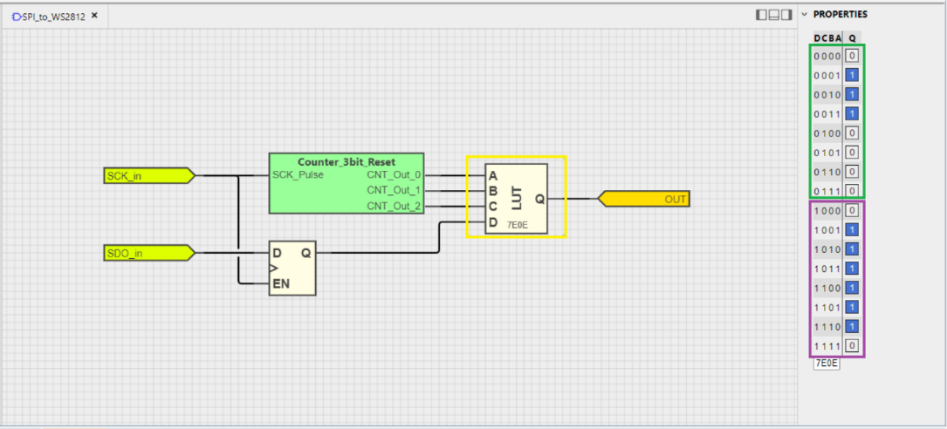

下一个示例是SPI至WS2812转换器。WS2812是一种单线串行协议,用于通过脉宽调制控制LED阵列。在本例中,SPI硬件用作要发送到LED的数据的移位寄存器,而CLB用于将SCLK和SDO转换为预期的输出。

在本例中,这是通过单触发3位计数器、带使能功能的D锁存器和4输入LUT来实现,如下面的图4所示。该实现的技巧体现在SPI和CLB的时钟源。SPI时钟设置为空闲高电平、在上升沿改变状态并以WS2812输出的频率(800 kHz)运行,而CLB的时钟源以前者10倍的频率(8 MHz)运行。当SCLK为低电平时,将触发3位计数器并开始计数。当计数到7(0b111)时,3位计数器将停止并保持为0,直到时钟脉冲的下一个低电平周期为止。

计数器的输出与输出数据的锁存版本一起馈入4输入LUT。这将设置数据的输出模式,如图4的右侧所示。计数器复位后,计数器输出将保持为0以完成循环。之后,可根据需要发送SPI硬件中的下一个字节,重复该循环。

图4——SPI至WS2812转换器框图(由Petre Teodor-Emilian开发)

这两个示例都证明了单片机内部分立逻辑的优势。硬件外设可将CPU从各种任务中解放出来,从而缩短响应时间并降低功耗,同时减少元器件数量。有了CLB,之前无法在单片机内部实现的复杂应用现在都可以顺利开发。目前,可前往Microchip直销网站或其他代理商处购买PIC16F13145系列单片机来获取CLB。

Robert Perkel是Microchip的一名应用工程师。他主要负责编辑应用笔记,投稿文章和视频等技术内容,以及分析外设的用例和开发代码示例与演示。Perkel毕业于弗吉尼亚理工大学,获得了计算机工程理学学士学位。