LPC1768时钟详解

2018-06-27 来源:eefocus

LPC1768有三个独立的时钟源,可以通过软件进行配置。MCU上电并成功复位后,内部的RC振荡器开始起振,并以此为工作频率去读取内部ROM区的代码来执行初始化工作,其中就包括对系统时钟的配置(在文件system_LPC17xx.c中)。

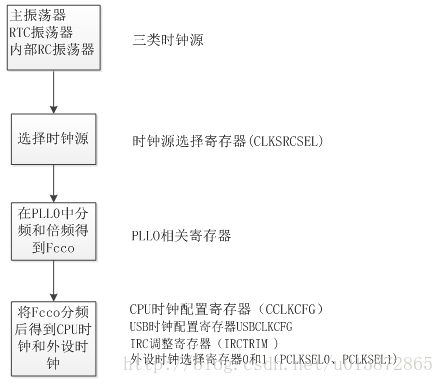

系统时钟配置的过程如下:

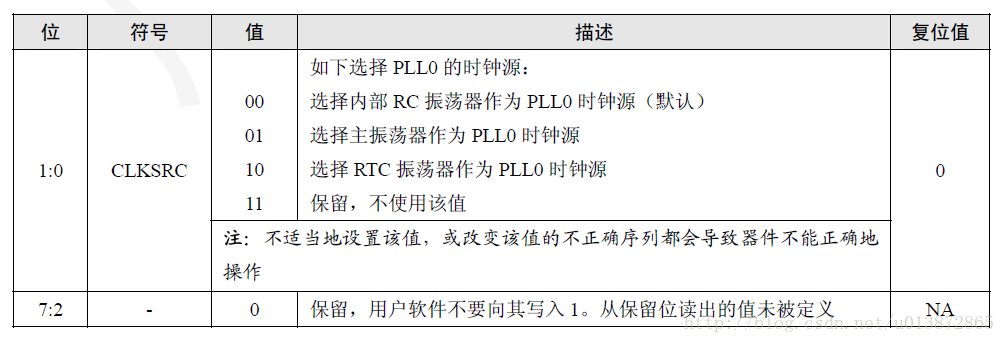

LPC1700系列Cortex-M3微控制器包括3个独立的振荡器,它们分别为主振荡器(通常指外界晶振)、内部RC振荡器和RTC振荡器。每个振荡器可根据特定的应用要求来选用(通过配置时钟源选择寄存器CLKSRCSEL),寄存器配置如下

表1 时钟源选择寄存器位描述

注意:注意下列有关时钟源选择的限制:

1. IRC的精度达不到USB接口的时间基准精度要求,因此IRC振荡器不应用作(通过PLL0)USB子系统的时钟源(USB要求一个占空比为50%的48MHz时钟源);

2. 如果CAN波特率高于100kbit/s,则IRC振荡器不应用作(通过PLL0)CAN控制器的时钟源

值得一提的是,LPC1768有一个专门针对主振荡器的寄存器叫作系统控制和状态寄存器(SCS),在选择主振荡器作为时钟源前,需要配置该寄存器。在该寄存器中可以配置主振荡器的频率范围、主振荡器使能,或读取主振荡器的状态(是否稳定)。位描述如下:

表2 系统控制和状态寄存器(SCS)位描述

时钟源确定后,PLL将输入时钟源升频,然后再分频以提供给CPU、外设或USB子系统使用的实际时钟。需要注意的是USB子系统有其自身特定的PLL(见“PLL1”的描述)。PLL0可产生的时钟频率高达100MHz,是CPU所允许的最大值。

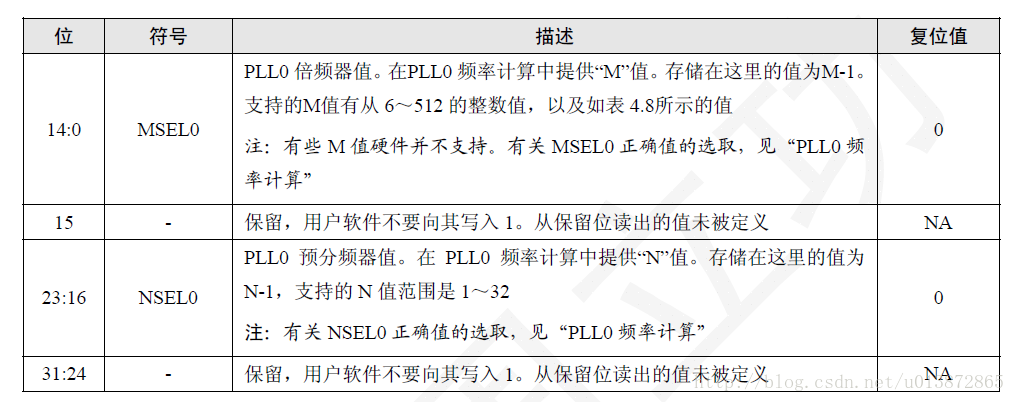

倍频和分频值通过写PLL0配置寄存器(PLL0CFG)中的MSEL0和NSEL0来改变,寄存器的位描述如表2.

表3 PLL0配置寄存器位描述

注意:在配置PLL0时必须将正确的馈送序列写入PLL0FEED寄存器才能使PLL0CON和PLL0CFG寄存器的更改生效。请参见手册PPL0馈送寄存器。

PLL0输出频率(当PLL0被激活且连接时)的公式:

Fcco=(2×M×FIN)/ N。

Fcco表示的是经过PLL0处理后输出的频率值,如果要为CPU和外设提供工作频率,还需要分别经过时钟分频器的分频,例如CPU时钟配置寄存器(CCLKCFG)、USB时钟配置寄存器(USBCLKCFG)等。

如果要用户根据需要自己配置M和N的值,请参见手册“计时和功率控制”一章中的确定4.5.11小节“PLL0频率参数的过程”。

在建立LPC1768的工程时,我们需要添加“system_17XX.c”文件,该文件主要的作用就是对系统时钟的配置,配置过程基本和本文一致。