ARM体系架构—ARMv7-A处理器模式及寄存器

2021-09-29 来源:eefocus

一、ARMv7-A处理器模式

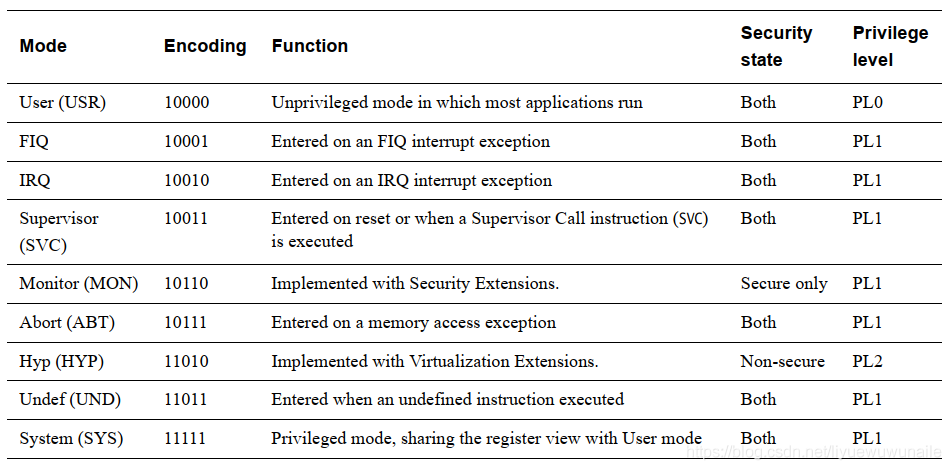

ARMv7架构支持安全扩展,如果使能了安全扩展,ARMv7-A架构分为安全模式(Secure State)和非安全模式(Non-secure State)两个世界。

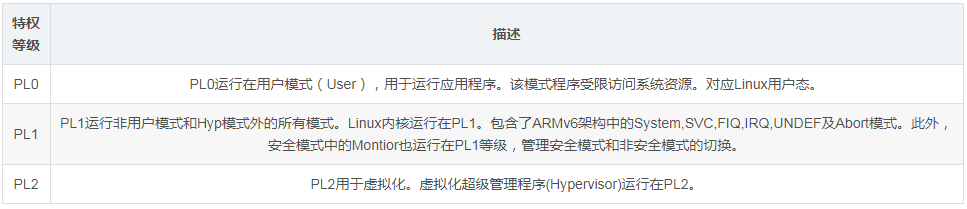

在非安全模式下,存在三种运行特权PL0,PL1和PL2(privilege level)。

If the Virtualization Extensions are implemented there is a privilege model different to that of previous architectures. In Non-secure state there can be three privilege levels, PL0, PL1 and PL2.

二、ARMv7-A通用寄存器

ARMv7-A架构提供了16个32位通用寄存器(R0-R15)和一个程序状态寄存器CPSR(Current Program Status Register),在异常模式下,可以访问SPSR(Saved Program Status Register),在异常模式下,SPSR用于保存当前CPSR寄存器值。其中R0-R14可以用于普通数据存储,R15是程序计数器PC(program counter)。

以上寄存器可能因运行模式不同而对应不同的物理存储位置,上图中蓝色区域即如此,它们使用不同的物理存储,通常只有在进程以特定模式执行时才可访问。

R0-R7在任何模式下都对应相同的物理存储,称之为未分组寄存器;

R8-R14根据模式不同对应不同的物理存储,称之为分组寄存器;

R13(SP)在User和Sys模式下对应相同的物理存储,FIQ,IRQ,ABT,SVC,UND,MON,HYP模式分别对应不同的物理存储。R13在ARM架构中用于SP堆栈指针(stack pointer)。MON模式用于管理安全与非安全模式,HYP模式用于管理虚拟操作系统(GuestOS)。

R14(LR)在User,Sys和HYP模式下对应相同的物理存储,FIQ,IRQ,ABT,SVC,UND,MON模式分别对应不同的物理存储。R14在ARM架构中用于LR链接寄存器,在每种模式下,R14用于保存子程序返回地址。执行BL指令时,R14用于备份R15寄存器的值。

R15(PC)保存当前程序执行的地址。在所有模式下,R15(PC)共享相同的物理存储。在ARM状态下,[1:0]为0,[31:2]用于保存PC。在Thumb状态下,[0]为0,[31:1]用于保存PC。

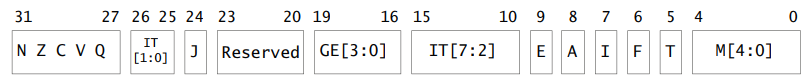

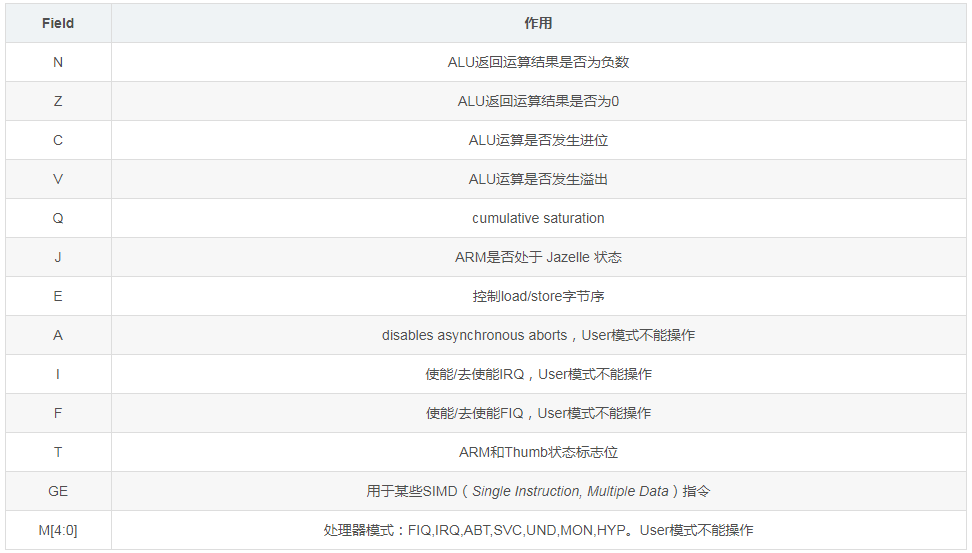

CPSR是程序状态寄存器,保存条件标志位,中断禁止位,当前处理器模式等控制和状态位。每种异常模式下还存在SPSR,保存进入异常模式前的CPSR寄存器值,用于异常处理完成后恢复CPSR的状态。User和Sys不属于异常模式,没有CPSR寄存器,在User模式下,受限的CPSR寄存器称谓APSR( Application Program Status Register)。ARMv7-A中CPSR寄存器的信息如下图所示。

各Field代表含义如下:

三、ARMv7-A协处理器CP15寄存器

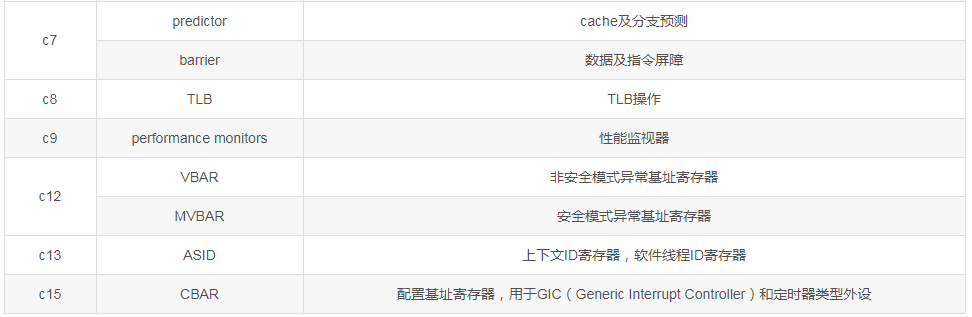

ARMv7-A架构保护系统控制协处理器CP15,主要用于处理存储系统相关的功能。CP15只能在特权模式下访问。CP15提供了16个32位主寄存器,命名为c0-c15。c0-c15寄存器可能对应多个不同的物理寄存器。

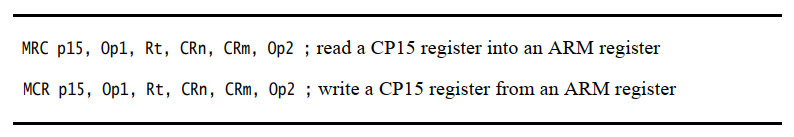

协处理器CP15寄存器访问包括读和写操作。

读操作即将CP15内的寄存器CRn的值读到通用寄存器Rt中,使用指令语法MRC, Op1, Rt, CRn, CRm, Op2;

写操作即将通用寄存器Rt的值写入CP15内的寄存器CRn中,使用指令语法MCR, Op1, Rt, CRn, CRm, Op2;

MRC:将CP15寄存器值读到ARM通用寄存器;

MCR:将ARM通用寄存器值写到CP15寄存器;

Op1 :协处理行为操作码;

Rt :ARM通用寄存器,不能是R15(PC);

CRn:协处理器CP15寄存器c0-c15;

CRm:附加目标寄存器,不需要附加信息,则设置为c0;

Op2 :区分同一编号不同的物理寄存器,例如分别访问c0中的MIDR和MPIDR,Op2值分别为0和1。默认情况下设置为0;

示例:

将CP15寄存器c0的MIDR寄存器读到R1中。

MRC p15, 0, R1, c0, c0, 0

四、系统控制寄存器CP15.SCTLR

系统控制寄存器SCTLR(System Control Register )用于控制内存,系统功能以及提供状态信息。

示例:

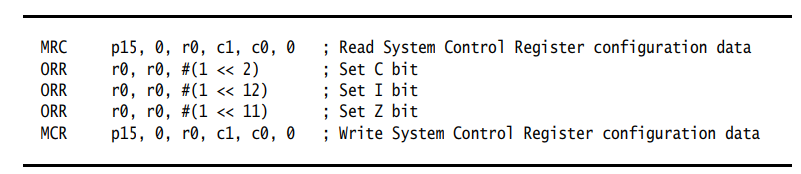

初始化CP15:SCTLR,使能Cache,指令Cache及分支预测功能。