MCS-51有4组8位I/O口:P0、P1、P2和P3口,P1、P2和P3为准双向口,P0口则为双向三态输入输出口,下面我们分别介绍这几个口线。

一、P0口和P2口

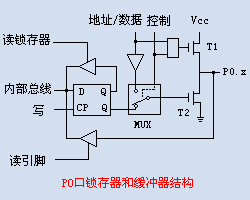

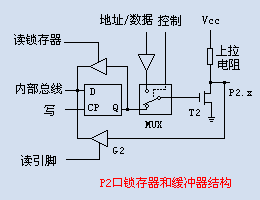

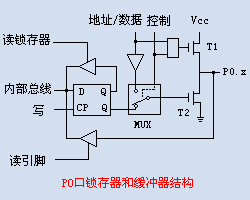

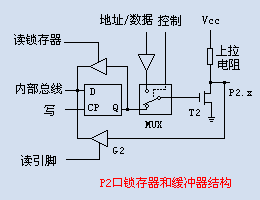

图1和图2为P0口和P2口其中一位的电路图。由图可见,电路中包含一个数据输出锁存器(D触发器)和两个三态数据输入缓冲器,另外还有一个数据输出的驱动(T1和T2)和控制电路。这两组口线用来作为CPU与外部数据存储器、外部程序存储器和I/O扩展口,而不能象P1、P3直接用作输出口。它们一起可以作为外部地址总线,P0口身兼两职,既可作为地址总线,也可作为数据总线。

图1 单片机P0口内部一位结构图

图2 单片机P0口内部一位结构图

P2口作为外部数据存储器或程序存储器的地址总线的高8位输出口AB8-AB15,P0口由ALE选通作为地址总线的低8位输出口AB0-AB7。外部的程序存储器由PSEN信号选通,数据存储器则由WR和RD读写信号选通,因为2^16=64k,所以MCS-51最大可外接64kB的程序存储器和数据存储器。

二、P1口

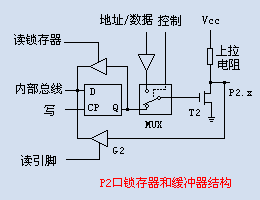

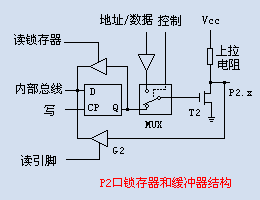

图3为P1口其中一位的电路图,P1口为8位准双向口,每一位均可单独定义为输入或输出口,当作为输入口时,1写入锁存器,Q(非)=0,T2截止,内上拉电阻将电位拉至'1',此时该口输出为1,当0写入锁存器,Q(非)=1,T2导通,输出则为0。

图3 单片机P2口内部一位结构图

作为输入口时,锁存器置1,Q(非)=0,T2截止,此时该位既可以把外部电路拉成低电平,也可由内部上拉电阻拉成高电平,正因为这个原因,所以P1口常称为准双向口。

需要说明的是,作为输入口使用时,有两种情况:

1.首先是读锁存器的内容,进行处理后再写到锁存器中,这种操作即读—修改—写操作,象JBC(逻辑判断)、CPL(取反)、INC(递增)、DEC(递减)、ANL(与逻辑)和ORL(逻辑或)指令均属于这类操作。

2.读P1口线状态时,打开三态门G2,将外部状态读入CPU。

三、P3口

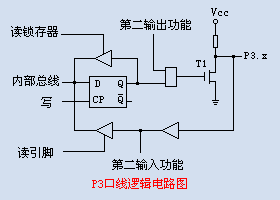

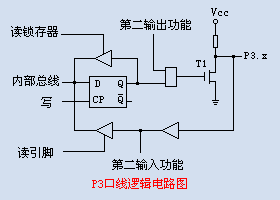

P3口的电路如图4所示,P3口为准双向口,为适应引脚的第二功能的需要,增加了第二功能控制逻辑,在真正的应用电路中,第二功能显得更为重要。由于第二功能信号有输入输出两种情况,我们分别加以说明。

图4 单片机P0口内部一位结构图

P3口的输入输出及P3口锁存器、中断、定时/计数器、串行口和特殊功能寄存器有关,P3口的第一功能和P1口一样可作为输入输出端口,同样具有字节操作和位操作两种方式,在位操作模式下,每一位均可定义为输入或输出。

我们着重讨论P3口的第二功能,P3口的第二功能各管脚定义如下:

·P3.0 串行输入口(RXD)

·P3.1 串行输出口(TXD)

·P3.2 外中断0(INT0)

·P3.3 外中断1(INT1)

·P3.4 定时/计数器0的外部输入口(T0)

·P3.5 定时/计数器1的外部输入口(T1)

·P3.6 外部数据存储器写选通(WR)

·P3.7 外部数据存储器读选通(RD)

对于第二功能为输出引脚,当作I/O口使用时,第二功能信号线应保持高电平,与非门开通,以维持从锁存器到输出口数据输出通路畅通无阻。而当作第二功能口线使用时,该位的锁存器置高电平,使与非门对第二功能信号的输出是畅通的,从而实现第二功能信号的输出。对于第二功能为输入的信号引脚,在口线上的输入通路增设了一个缓冲器,输入的第二功能信号即从这个缓冲器的输出端取得。而作为I/O口线输入端时,取自三态缓冲器的输出端。这样,不管是作为输入口使用还是第二功能信号输入,输出电路中的锁存器输出和第二功能输出信号线均应置“1”。

四、IO口工作原理

1. P0作为地址数据总线时,T1和T2是一起工作的,构成推挽结构。高电平时,T1打开,T2截止;低电平时,T1截止,T2打开。这种情况下不用外接上拉电阻.而且,当T1打开,T2截止,输出高电平的时候,因为内部电源直接通过T1输出到P0口线上,因此驱动能力(电流)可以很大,这就是为什么教科书上说可以'驱动8个TTL负载'的原因。

2. P0作为一般端口时,T1就永远的截止,T2根据输出数据0导通和1截止,导通时拉地,当然是输出低电平;要输出高电平,T2就截止,P0口就没有输出了,(注意,这种情况就是所谓的高阻浮空状态),如果加上外部上拉电阻,输出就变成了高电平1。

3. 其他端口P1、P2和P3,在内部直接将P1口中的T1换成了上拉电阻,所以不用外接,但内部上拉电阻太大,电流太小,有时因为电流不够,也会再并一个上拉电阻。

4. 在某个时刻,P0口上输出的是作为总线的地址数据信号还是作为普通I/O口的电平信号,是依靠多路开关MUX来切换的。而MUX的切换,又是根据单片机指令来区分的。当指令为外部存储器/IO口读/写时,比如 MOVX A,@DPTR ,MUX是切换到地址/数据总线上;而当普通MOV传送指令操作P0口时,MUX是切换到内部总线上的。

5. P0、P1、P2、P3口用于输入时,需要写1使IO下拉的MOS管截止,以免MOS管导通将输入拉底为0,当一直用于输入时不用置1(先使用该IO输出,该IO锁存器里可能是0,再用该IO输入则会使MOS管导通),将IO写1后,该IO锁存器不会变了,所以再一直用于输入不用置1。p0用于地址数据线时输入不用写1,因为MUX没和锁存器相连。

PS:

Because Ports 1, 2, and 3 have fixed internal pullups, they are sometimes called “quasi- bidirectional” ports.

因为端口1、2、3有固定的内部上拉,所以有时候他们被称为'准双向'口。

Port 0, on the other hand, is considered “true” bidirectional, because when configured as an input it floats.

端口0, 从另外一方面来说,就被 认为是'真正的'双向,因为当它被设置为输入的时候是浮空(高阻态)的。

五、P0口上拉电阻选择

如果是驱动led,那么用1K左右的就行了。如果希望亮度大一些,电阻可减小,最小不要小于200欧姆,否则电流太大;如果希望亮度小一些,电阻可增大,增加到多少呢,主要看亮度情况,以亮度合适为准,一般来说超过3K以上时,亮度就很弱了,但是对于超高亮度的LED,有时候电阻为10K时觉得亮度还能够用。我通常就用1k的。

对于驱动光耦合器,如果是高电位有效,即耦合器输入端接端口和地之间,那么和LED的情况是一样的;如果是低电位有效,即耦合器输入端接端口和VCC之间,那么除了要串接一个1——4.7k之间的电阻以外,同时上拉电阻的阻值就可以用的特别大,用100k~500K之间的都行,当然用10K的也可以,但是考虑到省电问题,没有必要用那么小的。

对于驱动晶体管,又分为PNP和NPN管两种情况:对于NPN,毫无疑问NPN管是高电平有效的,因此上拉电阻的阻值用2K~20K之间的,具体的大小还要看晶体管的集电极接的是什么负载,对于LED类负载,由于发管电流很小,因此上拉电阻的阻值可以用20k的,但是对于管子的集电极为继电器负载时,由于集电极电流大,因此上拉电阻的阻值最好不要大于4.7K,有时候甚至用2K的。对于PNP管,毫无疑问PNP管是低电平有效的,因此上拉电阻的阻值用100K以上的就行了,且管子的基极必须串接一个1~10K的电阻,阻值的大小要看管子集电极的负载是什么,对于LED类负载,由于发光电流很小,因此基极串接的电阻的阻值可以用20k的,但是对于管子的集电极为继电器负载时,由于集电极电流大,因此基极电阻的阻值最好不要大于4.7K。

对于驱动TTL集成电路,上拉电阻的阻值要用1~10K之间的,有时候电阻太大的话是拉不起来的,因此用的阻值较小。但是对于CMOS集成电路上拉电阻的阻值就可以用的很大,一般不小于20K,我通常用100K的,实际上对于CMOS电路,上拉电阻的阻值用1M的也是可以的,但是要注意上拉电阻的阻值太大的时候,容易产生干扰,尤其是线路板的线条很长的时候,这种干扰更严重,这种情况下上拉电阻不宜过大,一般要小于100K,有时候甚至小于10K。