台积电10 nm订单传出好消息 大幅节省成本

2015-03-18

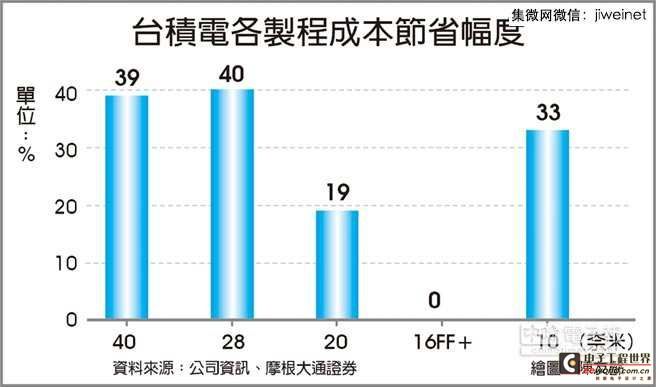

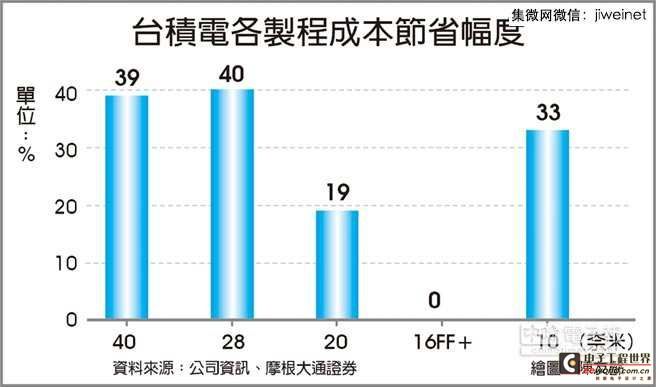

台积电各制程成本节省幅度

进入半导体设计/制造查看更多内容>>

昨(17)日传出,因台积电10nm制程技术大幅提升,先前在14奈米制程琵琶别抱英特尔的阿尔特拉(Altera),将在台积电与英特尔中择一作为10nm合作夥伴。外资法人认为,阿尔特拉订单若重回台积电怀抱,将是继去年拿下苹果A8订单后的另一项利多题材,投资价值将进一步攀升。

外资回头买超台积电

受此利多消息,外资昨天又回头买超台积电8,139张,暂时化解“卖台积电、转买三星”的潜在危机,台积电昨天以2.05%涨幅,略胜三星上涨1.84%。

摩根大通证券半导体分析师哈戈谷(Gokul Hariharan)表示,阿尔特拉在2013年2月宣布14奈米制程将与英特尔独家合作后,曾造成台积电本益比下修25%,由于近期台积电在10nm制 程技术提升大有斩获,阿尔特拉正决定10奈米合作夥伴会是台积电、还是英特尔,预计第一季将拍板定案。

哈戈谷指出,阿尔特拉所考量的点为下列3项:一、晶圆代工厂商的基础技术;二、晶圆厂商所能提供的服务;三、10nm产品能够提供的时间表。

哈戈谷表示,从近期台积电在半导体设备/EDA供应链所进行的10奈米制程技术与投资状况来看,想要迎头赶上英特尔的企图心相当强,事实上,以10奈米制程 所能节省的成本角度来看,10奈米对晶圆代工业者而言将是非常“大”的制程,相较之下,14/16奈米研发速度较慢,重要性也略低于10nm。

10nm大幅节省成本

哈戈谷指出,外界担心20nm以下高阶制程的成本节省空间有限,若拿20nm与40或28奈米比确实是如此,但因台积电10nm制程是由16nm FinFET+转换而来,相较于先前28nm转20或16奈米,可望节省更多成本,即便没有EUV,台积电10nm预估可较16nmFinFET+省下约 30%成本,整体而言,幅度和28nm与40nm相当,但优于20与16nmFinFET+。

显示能与英特尔一搏

欧系外资券商分析师指出,阿尔特拉10奈米订单若重回台积电怀抱,可望成为去年拿到苹果A8订单后的另一项大利多,对台积电营收、获利贡献虽然不若苹果来得大,但意味着10奈米已具备与英特尔一搏的条件,可望吸引更多客户投单。

相关文章

- 意法半导体披露 2027-2028 年财务模型及2030年目标实现路径

- 创实技术electronica 2024首秀:加速国内分销商海外拓展之路

- 欧洲三大芯片巨头,重新审视供应链

- 一场IC设计业盛宴!10场论坛 200位演讲嘉宾,300+展商亮相2万平米专业展会!

- 富昌电子于杭州举办技术日活动,聚焦新能源“芯”机遇

- 消息称铠侠最快明天获上市批准,市值有望达 7500 亿日元

- 美国政府敲定对格芯 15 亿美元《CHIPS》法案补贴,支持后者提升在美产能

- SK 海力士宣布量产全球最高的 321 层 1Tb TLC 4D NAND 闪存,计划 2025 上半年对外出货

- 三星电子 NRD-K 半导体研发综合体进机,将导入 ASML High NA EUV 光刻设备

最新频道

- A 65-nm CMOS Low Dropout Regulator Featuring 60-dB PSRR Over 10-MHz Frequency Range and 100-mA Load

- A Reconfigurable, 130 nm CMOS 108 pJ per pulse, Fully Integrated IR-UWB Receiver for Communication a

- 16-Element 4-Beam 1 GHz IF 100 MHz Bandwidth Interleaved Bit Stream Digital Beamformer in 40 nm CMOS

- A 10-bit 100-MSps Reference-Free SAR ADC in 90 nm CMOS

相关资料下载

最新器件