采用高性能SRAM提高DSP密集型应用的性能

2014-06-06 来源:互联网

数字信号处理

数字信号处理包含把信号转换成数字形式后对其进行处理的方法,如:雷达处理。雷达系统基本上是产生可以通过定向天线馈送的脉冲。这些信号以光速传播,而其路径中的任何物体都会把一小部分的投射能量反射回雷达接收天线。计算发送和接收信号的差别可以了解物体的距离与速度。

DSP是雷达系统的基础,可用于多种功能,如:脉冲压缩、信号滤波和脉冲调制。没有DSP,雷达系统就无法准确探测远距离的物体。DSP与通用的微处理器不同,因为它们适用于设计FFT和FIR等滤波器时最常用的快速数学计算(乘法与加法)类型。一般情况下FFT滤波器可用于域转换 – 从时域到频域或者相反,而FIR滤波器用于信号分离与恢复。这几种滤波器普遍存在于雷达设计中。

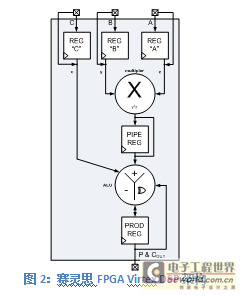

实现DSP有两种主要的硬件方法:可编程DSP处理器与现场可编程门阵列(FPGA)。在这两种方法中,DSP架构都非常适合DSP算法。

DSP处理器

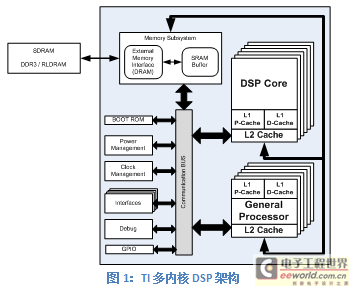

如图1所示的TI多内核DSP等DSP处理器采用专用硬件计算每个周期的乘法运算。现代DSP处理器的指令集允许编程人员在单个指令中指定多个并行运算,一般在主算术运算进行的同时一次或多次从存储器提取数据。另外,为了显著改善每个时钟周期的DSP性能,DSP架构目前包含并行运行的附加乘法器与加法器,从而可以在单个指令中编码并行运算。

DSP存储器需求

每个周期执行DSP函数都需要能够高效地从存储器提取指令与数据。因此,保持DSP性能的关键是高存储器带宽。DSP处理器和FPGA DSP块已经建立了内部高速缓存存储器架构(L1/L2),以支持每个周期多次的存储器存取。采用单独的存储器组存储指令与数据,可实现一种超级哈佛架构。处理器采用这种布置能够在每个周期并行提取指令与数据操作数。另外,DSP算法中的存储器存取一般呈现出可预测的模式。例如,FIR滤波器系数是按顺序循环存取。对于更深的外部存储,一般采用支持各种SDRAM存储器(DDR2/3、RLDRAM)、基于硬件的外部存储器接口(EMIF)。

为了使DSP性能提高两倍,可以实现采用QDR SRAM完成外部存储的最新创新性方法。

四倍数据速率(QDR)架构

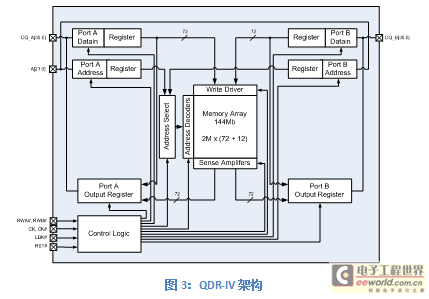

如图3所示赛普拉斯QDR-IV SRAM等SRAM是针对高吞吐量而精心优化的高性能存储器器件。此类存储器具有多个配备双数据速率(DDR)接口的独立数据端口。对这些数据端口的存取可同时进行并且相互独立。地址总线共用,并且根据相关配置以单或双数据速率运行。目前市场上密度最高的产品为144Mb,而且支持18倍或36倍配置。

QDR-IV SDRAM的架构特点非常有利于需要高吞吐量、低时延和真正随机存取的数字信号处理流程。

传统方法(SDRAM)与新方法(QDR-IV)对比

图4说明了测试环境的整体设置。采用基于FPGA的DSP功能对比不同存储器类型的最高数据吞吐量。

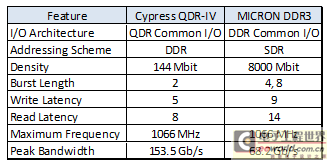

下表对比QDR-IV SRAM与DDR3 SDRAM存储器技术的主要性能参数。

本文引用地址:http://www.eepw.com.cn/article/247534.htm

表1说明了在相同频率运行时,QDR-IV可以提供超过DDR3 SDRAM两倍的带宽。此外,QDR-IV SRAM的双独立端口在获取输入信号的同时生成输出信号,易于满足DSP的实时处理功能对数据的需求。因此可以减轻向存储器传输数据以及从其提取数据时的瓶颈问题。

SAR雷达透视

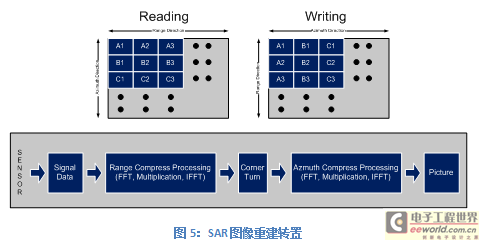

负责以高分辨率观察地表的SAR雷达需要进行转置存储器存取,其中对距离方向和方位方向进行转置,以便进行重建处理。距离与方位压缩处理之间的高效FFT与IFFT(DSP)运行可以实现此目的。QDR SRAM的架构优势能够通过实现快速、一致的存储器存取时间而提高SAR雷达的性能。图5说明了SAR图像重建相关的转置问题:

采用传统SDRAM存储器时,写入SAR图像数据(如图所示)会造成不连续的地址空间,从而导致处理器性能降低(此情况下估计大约降低5倍)。由于QDR-IV的独立读取与写入端口支持并行运算和随机存储器存取,因此可以降低对处理能力的影响。

QDR SRAM为基于DSP的应用中片外数据存储提供了对传统SDRAM的高性能替代方案。通过级联多个器件能够消除QDR SRAM的密度限制。由于能够实现速度更快的存储器存取而提高DSP性能,这种方法成为需要更高随机存取吞吐量的应用的理想选择。

- 如何使用Keil打开GD32 FPU及使用ARM DSP库 ?

- 苹芯科技全新边缘人工智能 SoC 使用Ceva传感器中枢DSP

- CS485xx数字音频DSP处理方案分析

- 六个术语(DAC、ADC、DSP、codec、运放、耳放)解析

- 人形机器人控制器之MCU、DSP、AI芯片

- 不只是高性能DSP,软件定义SoC给音频汽车工业等应用带来多通道和AI等丰富功能

- 基于DSP控制系统的离散模型参考自适应算法在燃料电池车中的实现

- 针对于DSP中关于提高实时检测效率的系统设计

- 恩智浦SAF9xxx音频DSP提升AI音频处理

- 天惠微2.4G蓝牙双模昆腾KT1200定制蓝牙DSP耳机收发模块PCBA