动态电压与频率调节在降低功耗中的作用

2007-06-18 来源:单片机及嵌入式系统应用

1 DVFS的工作流程

现在,为了延长便携式设备(如手机、MP3、多媒体播放器、笔记本电脑等)的电池寿命,芯片厂商们正在绞尽脑汁开发新的节电技术。简单地说,这些节电技术可以分为两类——动态技术和静态技术。静态技术包括不同的低功耗模式,芯片内部不同组件的时钟或电源的按需开关等。动态技术则是根据芯片所运行的应用程序对计算能力的不同需要,动态调节芯片的运行频率和电压(对于同一芯片,频率越高,需要的电压也越高),从而达到节能的目的。该技术的理论依据是如下的公式:

从上面的公式可以看出,降低频率可以降低功率,但是单纯地降低频率并不能节省能量。因为对于一个给定的任务,F*t是一个常量,只有在降低频率的同时降低电压,才能真正地降低能量的消耗。

目前许多芯片支持DVFS,比如InteI公司的芯片支持SpeedStep,ARM的支持IEM(Intelligent Energy Man-ager)和AVS(Adaptive Voltage Scaling)等。但是要让DVFS发挥作用,真正地实现节能,只有芯片的支持还是不够的,还需要软件与硬件的综合设计。

一个典型的DVFS系统的工作流程如下:

①采集与系统负载有关的信号,计算当前的系统负载。这个过程可以用软件实现,也可以用硬件实现。软件实现一般是在操作系统的核心调用中安放钩子,特别是调度器,根据其调用的频度来判断系统的负载。硬件实现如Frecscale的i.Mx31,通过采集一些核心信号中断线、Cache、内存总线的使用情况等,计算当前的系统负载。

②根据系统的当前负载,预测系统在下一时间段需要的性能。有多种预测算法可以选择,要根据具体的应用来决定。这种预测,既可由软件实现,也可由硬件实现。

③将预测的性能转换成需要的频率,从而调整芯片的时钟设置。

④根据新的频率计算相应的电压。通知电源管理模块调整给CPU的电压。这需要特别的电源管理芯片,比如Freescale公司的MC13783或者NS公司的支持Pow-erWise特性的系列电源管理芯片。它们能够支持微小的电压调整(25 mV)并且能在极短的时间内(几十μs)完成电压的调整。

另外,在调整频率和电压时,要特别注意调整的顺序。当频率由高到低调整时,应该先降频率,再降电压;相反,当升高频率时,应该先升电压,再升频率。

图1演示了简单的DVFS过程。

2 基于软件的DVFS实现

在基于软件的DVFS实现中,一般通过在操作系统的核心调用中安装钩子的办法来收集系统调用的信息,判断当前的系统负载。其中最重要的是调度器,其他地方包括读/写接口、定时器等。例如,在Linux内核中,一般在以下地方安装钩子。

◇kernel/sched.c。修改__schedule( ),在schedule( )前和后插入语句,记录一个任务的执行时间。

◇fs/read_write.c。修改sys_read( )和sys_write( ),记录其被某任务调用的次数。

◇kernel/timer.c。修改sys_nanosleep( )和msleep( ),记录任务主动休息的时间。

◇fs/ioctl.C。修改sys_ioctl( ),记录其被调用的次数。

◇kernel/exit.c。修改do_exit( ),记录任务主动退出的时间。

◇include/asm_xxx/system.h,arch/xxx/system.c。修改arch_idle( ),计算cpu_idle( )线程被调用的时间。

在预测下一时间段的系统负载时,需要利用采集到的前面几个时间段的实际负载值,然后根据下面的公式进行预测:

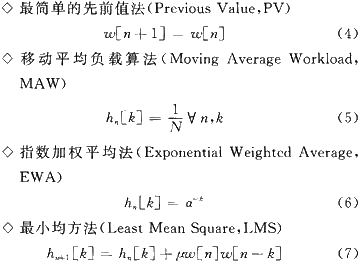

根据h的不同,可以形成不同的预测算法,比如:

以上这些算法各有其优缺点。例如LMS算法类似于自适应滤波器,能够自动调整参数,但是面临着收敛速度的问题。

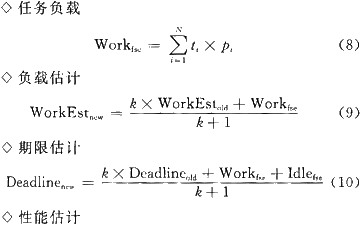

ARM公司为了验证其芯片的DVS(Dynamic VoltageScaling,动态电压调节)特性,开发的软件Vertigo中,采用了UH(Utilization History)算法,有关的公式如下:

![]()

该算法对那些性能需求变化较慢的任务比较实用,比如MPEG解码器。

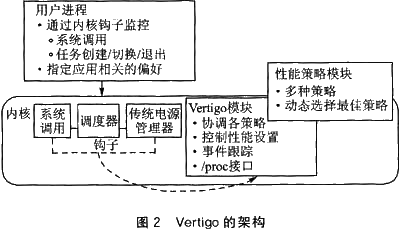

在Vertigo的实现中,一旦预测器完成性能预测,它将会把新的性能需求提交给策略管理器,由策略管理器决定是否调整当前的性能设置。Vertigo的架构如图2所示。

具体实现可以参阅文献[3]。

3 基于硬件的DVFS实现

正如前面所说的,CPU负载跟踪与性能预测的工作都可以由硬件完成。这样,一方面增强了负载计算的准确性;另一方面减轻了CPU用于负载跟踪与性能预测的负担。当然,这样做也有一个弊端,就是无法灵活地选择预测算法。但是,这个缺点可以通过设置不同的预测参数得到一定程度的弥补。

飞思卡尔的i.MX31就是这样的一个例子。这是一款针对移动多媒体市场的应用处理器,具有强大的音频和视频处理能力。该芯片内部包含一个ARMll的CPU核,同时它也继承了来自ARM的DVS技术并发展为DVFS。在该芯片中,CPU负载跟踪和性能预测都是由硬件完成的,其负载跟踪模块框图如图3所示。

在图3中,16路CPU活动信号被采集之后,经过加权,被送到负载叠加器,与另外采集的CPU空闲信号(经过简单平均)进行叠加。叠加器输出的结果被送到EMA模块,执行指数移动平均(Exponential Moving Average)算法,进行性能预测。EMA模块得到的结果与预先没置的门限值进行比较,如果预测的性能需求高于上限,则请求调高频率;反之,如果预测的性能需求低于下限,则请求降低频率。这种请求一般作为中断,发送给CPU自身或外接的处理器,由它们在其中断处理程序中设置相应的频率和电压。图4演示了整个处理流程。

在图4中,CCM(Clock Control Module)为时钟控制模块,负责涮节CPU的频率。PMIC(Power ManagementIC)为电源管理芯片,负责提供CPU所需要的电压。该芯片提供两种接口给CPU:常规的SPI(Serial ProgrammableInterface)和专用于动态电压调节的DVS接口。该接口由两根线组成。两根线的状态00表示电压无变化,01表示电压降低一格,10表示电压升高一格,11表示电压升到最高值。

图4中的DPTC(Dynamic Process and TemperatureControI)指的是动态制程与温度控制。该技术能够根据该芯片的制程和当前的温度动态调节电源电压,从而也可以有效地节省能量。这也是i.MX31的一项创新。

4 DVFS应用的实际效果

为了验证DVFS的实际效果,需要在CPU上运行相应的应用程序,并测量使用DVFS技术和不使用DVFS技术时CPU的功耗。这里,分别给出软件实现的DVFS和硬件实现的DVFS在节省能量方面的实际测量数据。

Intrinsyc公司将ARM公司的IEM软件移植到WinCE上,并测量了IEM使能或禁止时的CPU功耗。软件运行在i.MX31的开发板上,但是因为它没有使用i.MX31内置的DVFS,因此可以将其看作软件实现的DVFS。在计算CPU负载时,采用了简单移动平均算法(即式(3)中的h恒为1/N);同时,它通过一个GPIO来指示系统是否已经进入空闲状态(cpu_i-dle()线程被调度)。如果Idle的比例越小,则表明CPU的利用率越高。表l和表2是实际的测量数据。

为了验证硬件实现的DVFS的功效,作者在i.MX31的开发板上进行了测量。所使用的操作系统是Linux。表3给出了实际的测量数据。

从表3中可以清楚地看出,无论软件实现的DVFS还是硬件实现的DVFS,都可以有效地降低能量消耗。

5 影响DVFS应用的因素

动态电压与频率调节的技术提出很久了,在Linux上也有专门的开源项目cpufreq,但是这项技术并没有得到广泛的应用。其中一个最关键的因素就是预测的可靠性。没有一种预测算法是100%准确的,也没有一种算法可以应用于所有的程序;而对于实时类的应用(如音频、视频等),预测失败的结果是不可接受的。因为实时类的应用都有一个Deadline,错过Deadline,就意味着程序的运行出了问题。比如音频或视频帧的播放时间错过以后,用户就能明显地感觉到音频或视频的不连贯,这会极大地影响用户的体验,从而也会影响用户对DVFS的信心。作者在进行DVFS的测试时,就碰到过这些问题。IEM测试中采用的简单移动平均算法只对单一应用程序有效。但是i.MX31内置的移动指数平均算法EMA也不是万能的。对于Pink Floyd的某些音乐,它就不能平滑地播放(也许通过修改一些加权参数,可以播放)。

但是作者相信,随着预测算法的进步,DVFS技术必将得到广泛的应用,因为它能够节省很多能量。而节能对许多便携式设备来说,常常是第一要求。

上一篇:基于单片机的通用型智能充电器设计

下一篇:如何为变化的负载阻抗提供恒定功率

- 行业首次!小鹏宣布P7车机芯片众筹达成:升级骁龙8295 流畅度翻2倍

- 创新不止 美芝、威灵亮相2024中国家用电器技术大会

- 越南芯片封测业务增长 供给侧碎片化正在分裂市场

- Melexis推出超低功耗车用非接触式微功率开关芯片

- 美方要求台积电限制出口高端芯片,商务部回应

- 高功率、多协议,南芯科技车载充电芯片家族又添两大产品

- AMD将裁员4%,以在人工智能芯片领域争取更强的市场地位

- 里程碑式进展!思特威CMOS图像传感器芯片单月出货超1亿颗!

- Microchip推出新型VelocityDRIVE™软件平台和车规级多千兆位以太网交换芯片,支持软件定义汽车

- 汽车芯片封装技术工艺流程科普

- 祛魅固态电池:一文看懂这项大火的技术