作者:德州仪器Aaron Paxton

在我的上一篇博文LDO基础知识:噪声 – 第1部分中,我探讨了如何减少输出噪声和控制压摆率,方法是为参考电压(CNR/SS)并联一个电容器。在本篇博文中,我将讨论降低输出噪声的另一种方法:使用前馈电容(CFF)。

什么是前馈电容?

前馈电容是一个可选的顶容器,与电阻分压器的上半部电阻并联,如图 1 所示。

图 1:使用前馈电容的NMOS低压差稳压器(LDO)

与降噪电容(CNR/SS)相似,添加前馈电容具有多种效果。最主要的是降噪,还包括改进稳定性、负荷响应和电源抑制比(PSRR)。(应用报告“使用前馈电容的低压差稳压器的优缺点,”详尽讨论了这些益处。)值得注意的是只有使用可调节LDO时才能使用前馈电容,因为此时电阻网络在外部。

降噪

LDO进行调节时会使用误差放大器,而误差放大器会使用电阻网络(R1和R2)来提高参考电压的增益,从而驱动FET的栅极,这与同相放大器非常相似。参考的直流电压将增加???倍。不过,考虑到误差放大器的带宽,您还可以寄望于参考电压某些交流元件的放大功能。

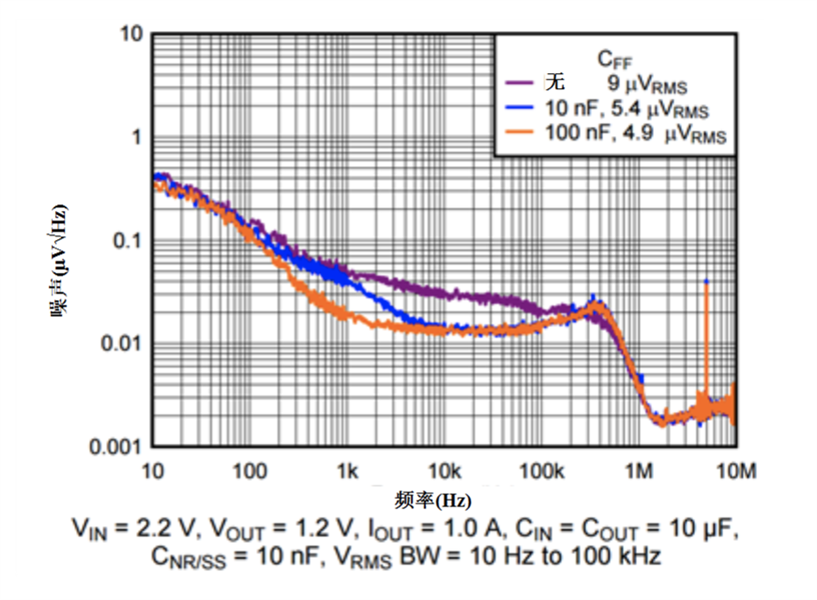

通过为电阻分压器上半部分电阻并联电容器,您就针对特定频率范围引入了一个分流器。换言之,您使该频率范围内的交流元件贡献于单位增益,此时R1模拟短路的情况。(请牢记所用电容器的阻抗属性,以便确定该频率范围。) 如图 2 所示,您可以看到使用不同CFF值时,TPS7A91的噪声下降效果。

图 2:TPS7A91噪声 vs. 频率和CFF值

通过为电阻分压器上半部分电阻并联一个100nF电容器,可将噪声从9μVRMS降至4.9μVRMS.

改进稳定性和瞬态响应

添加一个CFF还为LDO反馈环路引入了零点(ZFF)和极点(PFF),它们的计算见等式 1 和 2:

ZFF = 1 / (2 x π x R1 x CFF) (1)

PFF = 1 / (2 x π x R1 // R2 x CFF) (2)

在达到发生单位增益的频率之前就形成零点,可以改善相位裕度,如图 3 所示。

图 3:仅使用前馈补偿的典型LDO的增益/相位图

您可以看到如果没有ZFF,单位增益的发生大约将提前约200kHz。通过添加零点,单位增益频率向右移动了一点(~300kHz),但是相位裕度也增加了。由于PFF位于单位增益频率的右侧,所以它对于相位裕度的影响也最小。

在改进LDO的负荷瞬态响应后,将看到相位裕度的明显增加。在相位裕度增加后,LDO输出将减少振铃并更快速稳定。

改善PSRR

取决于零点和极点的设置,您还可以巧妙减少增益漂移。图 3 显示了零点对从100kHz开始的增益下降的影响。通过提高频段内的增益,您还将改进该频段的环路响应。这会改善该特定频率范围的PSRR。参见图4。

图 4:TPS7A8300 PSRR vs. 频率和CFF值

如图所示,增加CFF电容值,会将零点推向左侧。催生较低频率范围内产生更佳的环路响应和相应PSRR。

当然,您必须选择CFF值和适当添加零点ZFF和极点PFF,这样才不会造成不稳定。遵守上面这个数据表给出的CFF限值,即可防止不稳定情况的出现。大电容值CFF会造成前述应用报告介绍的其他问题。

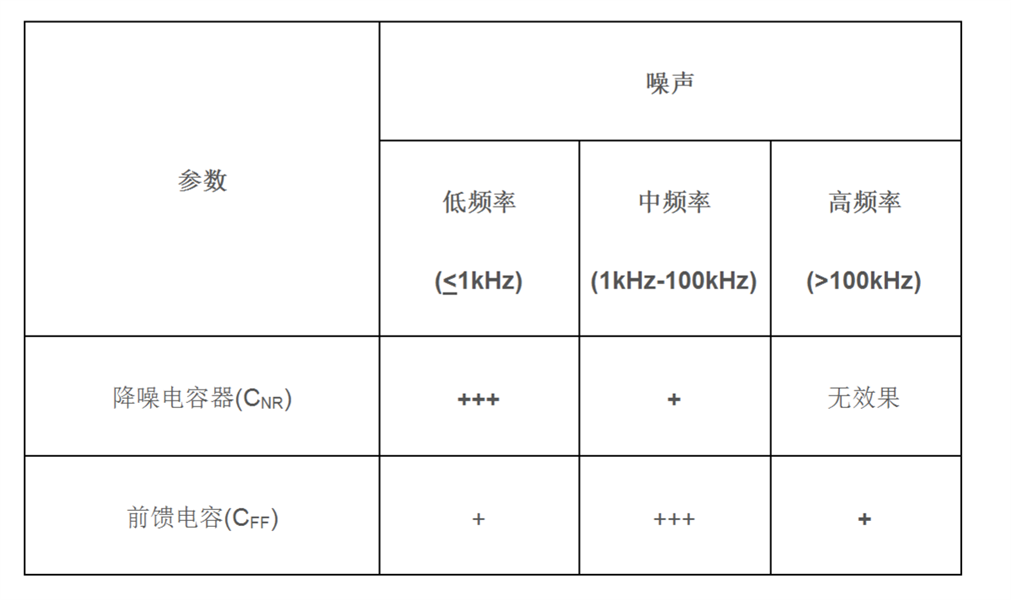

表 1 列出了有关CNR和CFF如何影响噪声的经验法则。

表 1:CNR和CFF vs 频率

结论

正如本文论述的那样,添加一个前馈电容可降噪,改进稳定性、负荷响应和PSRR。当然,您必须仔细选择电容器才能维持稳定性。如果采用降噪电容器,交流性能将获得大幅改善。这些是您需要牢记以便优化电源的几个方法。