近日,朋友遇到一个关于mosfet 开关的问题。虽然问题已经轻松解决,但后来仔细想想,背后的知识点却是比较基本和重要的。联想到目前年轻的工程师见到的越来越多的是集成的开关器件,对这些基本元件的特性可能压根就没怎么在意。今天刚好就这问题,浅析一下mosfet的开关特性。

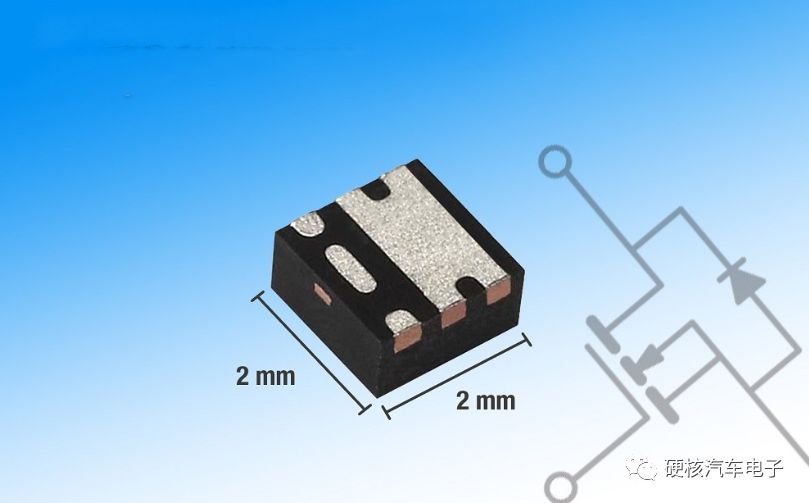

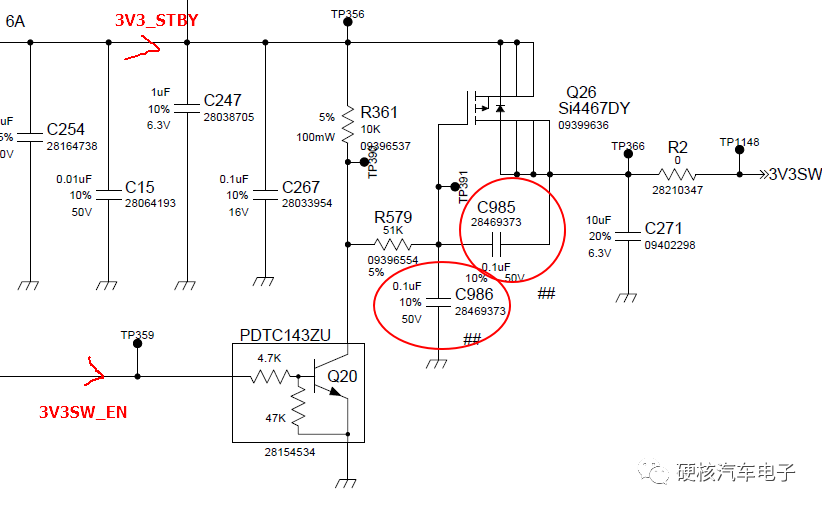

问题的背景如下,这是一个等电压转换开关。由单片机去控制从3V3STBY到3V3SW的pmos 开关。

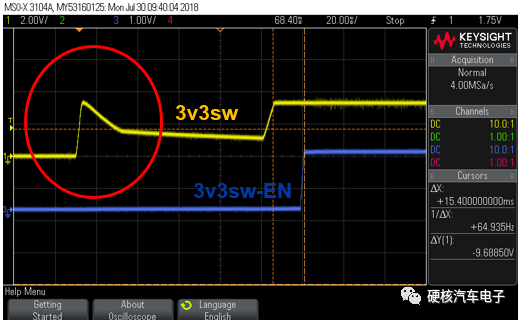

如下图,power on的过程中3V3SW power rail, 有一个voltage dip. 对比3V3SW_EN(blue),发现在turn on 控制信号到来之前,3V3SW上就有电压了。

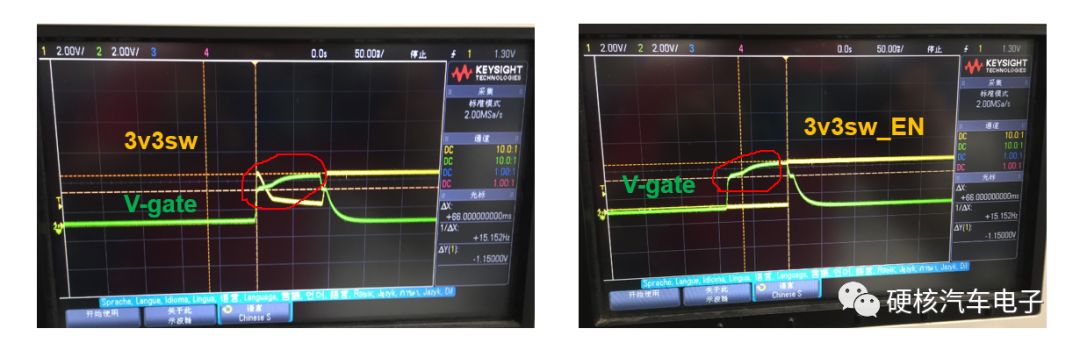

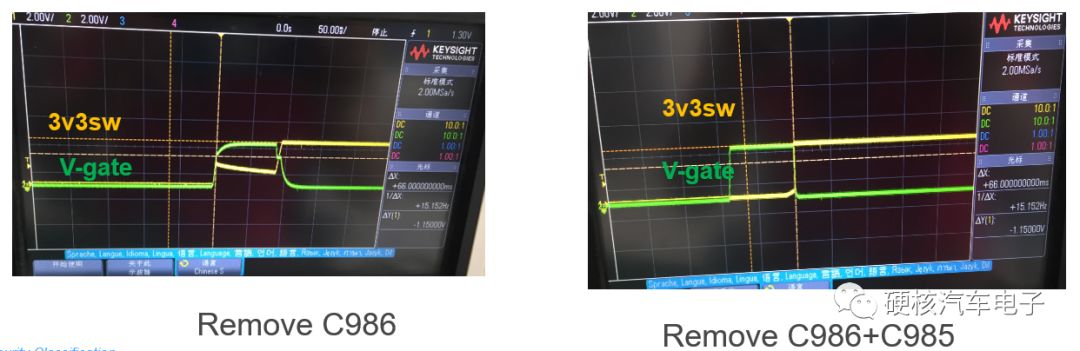

示波器测量发现,3V3SW_EN控制信号pull high之前,mosfet gate电压(green)和3V3之间有1.1V左右的gap, 原则上在控制电压到来之前Vgate=3V3, 这样Vgs<Vth, mosfet不导通。

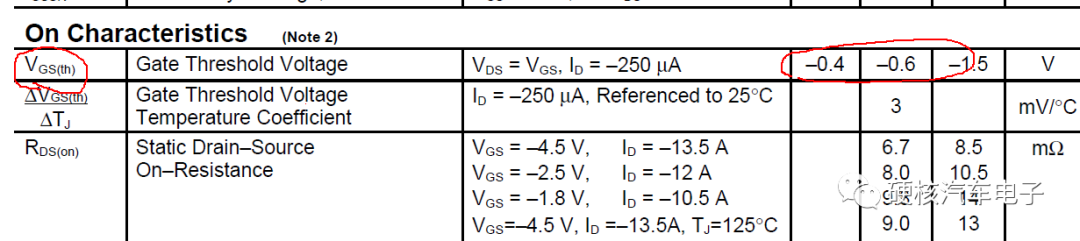

查阅mosfet 手册,Vth最小0.4V。由此可见,Vgs之间压差导致漏电。

去掉电路中的C986和C985之后,问题得到解决(最终方案C985换成了1nf的小电容)。

上面的问题比较容易就解决了,但背后的知识点却是比较重要。这就是mosfet的开关特性。

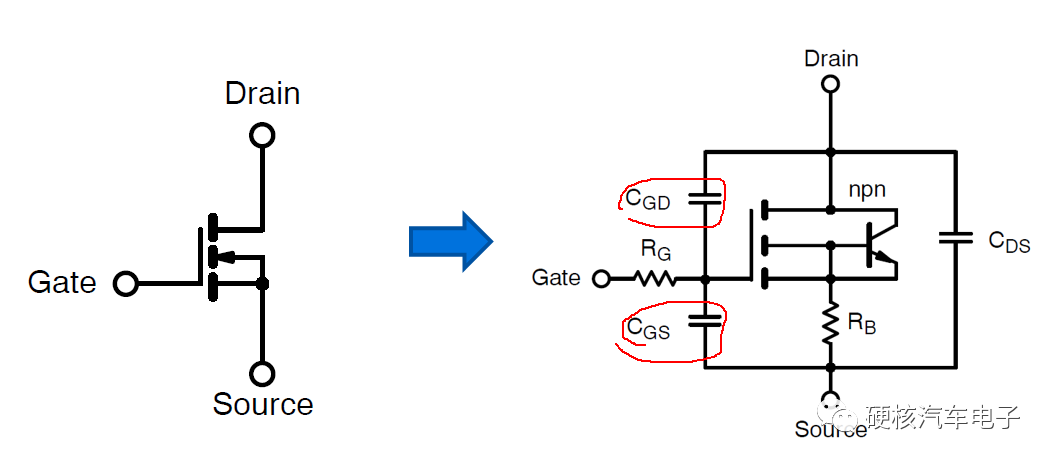

如下是mosfet的等效模型,Gate 和Drian、Source之间分别有寄生的电容Cgd和Cgs。这两个寄生电容直接影响着mosfet的开关特性。

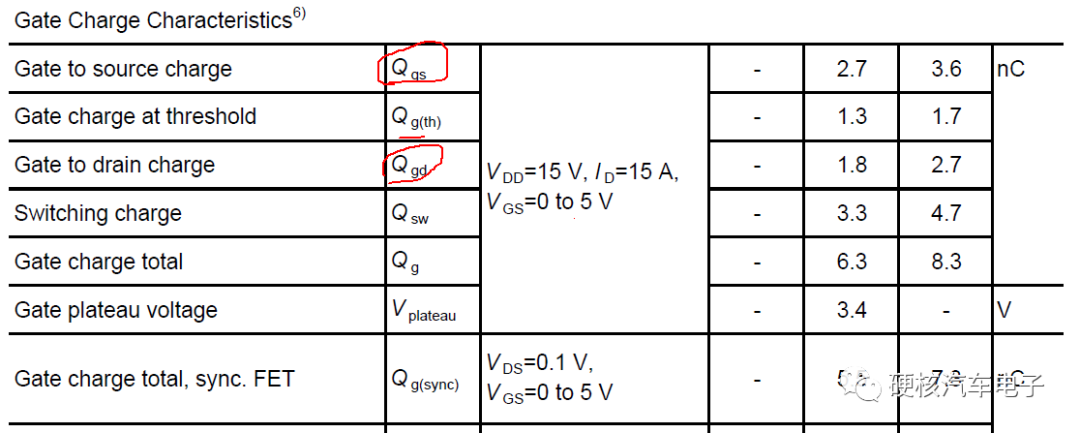

有些mosfet手册上关于这两个寄生电容用Q来表示。

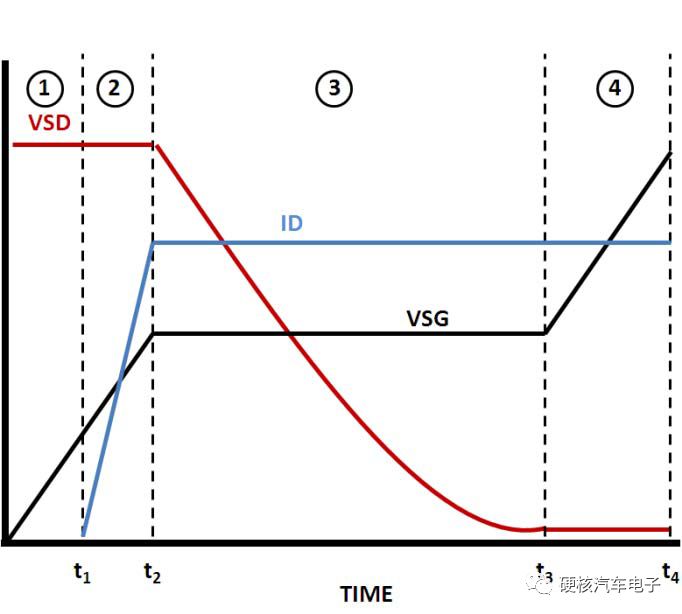

下图是Mosfet trun on的整个过程:

Total 分为4个区域

Region 1, VGS 开始增加,这个时候还没有到达Vth, 所以VSD保持不变,ID还是零。t1时刻,VGS=Vth

Region2, VGS 达到Vth以后, mosfet 开始导通,ID开始有电流。由于gate和source之间寄生电容的存在,gate的电压开始给Cgs充电,,达到t2的时候,Cgs 冲满,VGS达到稳定值,ID达到最大。

Region3, VGS继续保持不变,Cgd开始充电,VSD之间的压差开始减少,到达t3的时候,Cgd充满了,VSD压差几乎到达最小值,这个时刻mosfet 完全导通。

Region4, VGS持续增大到驱动电压,VSD之间的压差=Rdson*ID.

从这个过程可以看到,如果要控制VSD的slew rate 可以控制region3的时间。Cgd增大,VSD slow rate就越小,当然in-rush current 也越小。当然这也是为什么最上面的电路drain和gate之间有一个电容的原因,考虑到mosfet本身的寄生Cgd可能会比较小,增加这样一个电容可以控制开关的slew rate.

回到上面的问题,由于电路中C985 C986都放了0.1uf,比较大,3V3STBY上升的过程中Gate电平没有快速达到3.3V,导致漏电。减少容值,可解决问题。

在有些电路中为了避免上述问题,可以加一个二极管快速导通使gate电压快速达到和source一致。

理解mosfet的rurn on 过程才能深刻理解mosfet的各种应用。无论是在开关电路和时DCDC电路都需要考虑mosfet的开关特性。

声明:

以上仅为个人观点。

相关资料来源网络。