历史上的今天

今天是:2025年03月15日(星期六)

2018年03月15日 | DDS+PLL组合方案实现的频率合成系统

2018-03-15 来源:eefocus

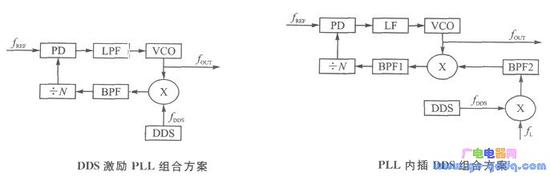

用DDS+PLL组合方案实现的频率合成系统可以获得高的频率分辨率、快速转换及较宽的频率范围,满足各方面需要的频率。合成器的基本思想是用一个低频的DDS激励一个PLL倍频系统,实现高的频率分辨率、高的转换速率和较宽的输出频率。

1.DDS激励PLL的锁相倍频方案

该方案用DDS输出作为PH倍频的激励信号PLL,设计成N倍频环,如图1所示。通过采用高的鉴相频率来提高PLL的转换速度,并利用DDS的高频率分辨率来保证倍频PLL,以实现较高的频率分辨率(N△φ×js/2m其中M、fs分别为DDS的相位累加器的位数和时钟频率),同时PLL环路的带通滤波性能可以对DDS的带外杂散起抑制作用。该方案的优点是电路结构简单,成本低,易于控制,易于集成。由于PLL用于倍频,因此落在环路噪声带宽内的DDS输出信号中的相位噪声和杂散成分将倍增2010gN dB。所以采用此方案时,如果为了保证频率转换时间,环路带宽取得较大,则N值就不能取太大。一般取N<10,从而保证系统的噪声性能。

2.PLL内插DDS的组合方案

这种组合方案如图2所示,其输出频率

![]()

要求fREF≤BWDDS。在这种方案中,由于DDS具有很高的频率分辨率,因而PLL可采用高的鉴相频率REF,从而提高PLL的频率转换时间。由于DDS的输出不经PLL倍频,因而DDS输出的相位噪声和杂散不会在输出端恶化,所以该方案具有低的相位噪声和优良的杂散性能。其缺点在于BPF设计困难.因为OUT值越大,fOUT -fDDS与fOUT+fDDS的距离就越近,这就要求BPF有严格的g滚频特性。为了解决这一问题,可以采用图4所示的改进方案。先用本振fL与DDS相混频,将DDS的输出搬到相对高的频率上,这样就降低了BPF的设计难度。该方案保持了图3方案的优点,但多了一个混频环节,使硬件复杂度提高,调试困难度加大,因为混频在输出中会带来一定的寄生分量。

由以上分析看出,DDS激励倍频PLL的方案电路结构最简单,所用的硬件最少,在输出频段一定时,可尽可能提高DDS的输出频率(采用高时钟频率的DDS),从而提高PLL的鉴相频率。这样,既可提高跳频速度,又可减小倍频数N以防止噪声性能的严重恶化。廉价的CMOS工艺DDS产品可以输出十几MHz的信号,只需几倍倍频即可达到VHF波段。PLL在10 MHz的鉴相频率时,可实现几十μs的跳频速度,因而这种方案尤其适用于VHF波段的跳频频率合成器或覆盖该频段的高分辨率的频率源。

下一篇:DDS+PLL频率合成技术与应用

史海拾趣

|

德国mandia大功率LED专用荧光粉 一、简介 德国mandia大功率LED荧光粉是(Deutschland Mandia Materials Development Co., Ltd)德国mandia公司应对新世纪的照明工业的发展研制而成,该产品粒径15±0.1mil,适用于450-470NM芯片,亮度与市场上小功率 ...… 查看全部问答> |

|

下面是处理电源irp的代码节选,问题是:为什么提高电源级别时使用完成例程,而降低电源级别时直接使用PoSetPowerState( pDevObj, type, newState);?请高手赐教! if (newState < pDevExt->currentPowerState) {& ...… 查看全部问答> |

|

请问各位高手和大侠!! 怎么样才能入门CAN-BUS,小弟现在看了关于CAN-BUS的书籍,但是就是不明白里面协议,请高手指点,怎么入门,会编写程序,会应用?… 查看全部问答> |

|

uC/OS-II官方STM32版本修改后在万利的STM32开发板上运行 bh3nvn:您好,学习单片机和ARM也都四五年了,我本身电气工程毕业的,所以操作系统的东西一直没时间琢磨,也一直想 ...… 查看全部问答> |

|

STM32固件库的CMSIS简析 [ 2011-2-23 11:26:00 | By: banyai 2011-8-19 Edit By:tony STM32的V3.3.0库,内有CMSIS的文件夹为arm Cortex微控制器软件接口标准,现在 ...… 查看全部问答> |

|

美高森美推出IGLOO2拓宽FPGA产品组合,Actel的SmartFusion换了个马甲 IGLOO2 FPGA提供最低系统成本、业界最佳集成度、低功率、高可靠性和安全性美高森美公司(Microsemi Corporation,纽约纳斯达克交易所代号:MSCC) 现在宣布推出用于工业、商业、航空、国防、通信和安全应用的IGLOO®2现场可编程门阵列(FPGA) ...… 查看全部问答> |