历史上的今天

今天是:2024年10月18日(星期五)

2018年10月18日 | 2020年正式开启大容量内存时代?美光宣布DDR5明年量产

2018-10-18 来源:爱集微

当前显卡显存已经发展到GDDR5X和HBM2,而DDR4系统主存仍在普及过程中,我们不难看到DDR3的内存仍旧有着活跃的身影。不过,去年四月内存标准指定机构JEDEC表示新规范已开始着手,DDR5内存标准将在明年完成。

虽然到目前为止DDR5的标准规范仍在制定过程中,但Cadence于今年5月已宣布业内首个DDR5内存的IP接口芯片,包括控制器和PHY物理层,采用台积电7nm工艺制造,运行频率达4400MHz,相比目前商用最快的DDR4-3200快将近37.5%。正如DDR4内存频率从2133MHz一路走到3200MHz,4400MHz对于DDR5来说可能只是个起步,预计最终可达到6400MHz左右,为了支持Cadence,美光向其提供DDR5内存初步版本的工程原型。

5个月过去了,美光的DDR5终于迎来了新的消息。据悉,Cadence和美光已经开始研发16Gb容量的DDR5产品,并计划在2019年底量产。据美光最新说法,其DDR5产品基于18nm以下工艺,搭载该内存的系统预计最快2020年问世。

16Gb也许只是个开始,未来单条大容量内存的时代将会开始,据悉DDR5内存允许加入内部ECC来制造16Gb,32Gb颗粒,单条容量也会大大提升,其他改进将会有电压降低、每通道32/40位(ECC)、总线效率提高、增加预取的Bank Group数量以改善性能等。

在此之前,Rambus也曾提过7nm工艺下的DDR5 IP,并预计DDR5内存要到2020年才会商用。Cadence Analysis预计第一套DDR5内存系统将于2019年面世,然后迅速普及,2022年就能达到25%左右的渗透率。

值得注意的是,AMD曾保证说现在的AM4接口将会一直支持到2020年。这是否预示着DDR5将会在2020年正式出山呢?

史海拾趣

|

rotel DXP2004教程(原理图,PCB)下载 [ 本帖最后由 shuijian 于 2008-10-21 17:23 编辑 ]… 查看全部问答> |

|

可编程霓虹灯图形动态广告控制器的设计 摘要 本文结合国内外霓虹灯控制技术的发展状况设计了一种采用美国ATMEL公司生产的AVR系列单片机中的ATmega8作控制芯片的霓虹灯控制器.通过ATmega8芯片控制驱动电路,在由驱动电路驱动继电器,而继电器则作 ...… 查看全部问答> |

|

1.电路板(除去元器件)由什么材料制成? 2.电路板用PROTEL画图的时候,哪些层分别对应着哪些位置?(比如;topoverly,layout...) 3.什么是波峰焊,回流焊?… 查看全部问答> |

|

看过版主大神的大作,想自己也实践一下,不过发现有个低端问题,求问,SD卡不是共有九个脚吗,要怎么跟LPC1114连接呢?哪个对应那个?(其实版主大神的图我没看懂,我承认我很弱。。。。。。):L … 查看全部问答> |

|

相信很多高手用TI的图形库,各个空间用起来是方便了许多!今天准备在不同的控件界面下,显示例如时间这类不断需要更新的东西,而在不同的图层下需要动态循环显示的内容是不一样的。因为经验缺乏,我现在用的方法觉得很死,就是利用一个变量,看这个 ...… 查看全部问答> |

|

前仿真出来的状态机时钟正确的, 而后仿真出来的状态机中,有些状态之间就会有很短时间的其他状态,时间不到系统时钟的十分之一。 上图是后仿真时序,状态3后应该是状态4,但是实际却是状态7 和 6 ,而且时间很短,不到一个时钟周期,这导致了后 ...… 查看全部问答> |

|

module bianma(in,EI,EO,GS,out); input [7:0] in; input EI; output EO,GS; output [2:0]out; reg [2:0]out; reg EO,GS; always @(EI,in) if(EI) case(in) 8\'b11111110: begin out=3\'b111;GS=0;EO=1;end 8\' ...… 查看全部问答> |

|

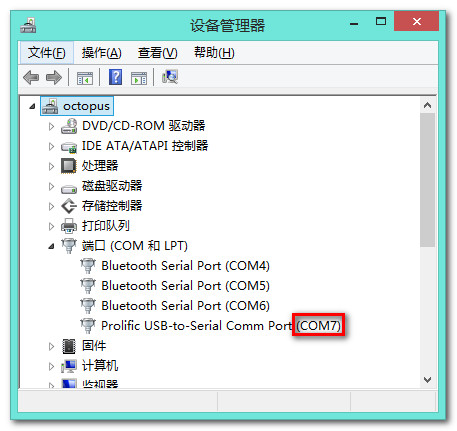

基于LABVIEW和RL78评估板的心电图采集系统 创意进度贴+ RL78/G14 DEMO使用 基于LABVIEW和RL78评估板的心电图采集系统 创意进度贴+ RL78/G14 DEMO使用 收到板子后就把程序安装了,先用下DEMO程序,启动界面选择COM4连接,可以看到检测数据状态输出,截图如下: 在此可以查看内存数据: 在此可以做自检: 编程环境CubeS ...… 查看全部问答> |