历史上的今天

今天是:2024年09月24日(星期二)

2019年09月24日 | PCIe Gen4与UPI互联 英特尔出货Stratix 10 DX FPGA

2019-09-24 来源:EEWorld

“它的独特之处就是高带宽以及低时延,该产品是英特尔首个支持PCIe Gen4的FPGA,同时它采取了超路径互连UPI。”近日,Stratix 10 DX FPGA产品正式向合作伙伴出货。英特尔公司网络和自定义逻辑事业部副总裁兼FPGA和电源产品营销总经理Patrick Dorsey先生,就新产品以及未来的产品规划,接受了EEWorld记者的采访。

搭配UPI性能全面提升

Stratix 10 DX FPGA支持英特尔超路径互连(UPI)和PCI-Express (PCIe) Gen4 x16,同时还支持英特尔傲腾技术来提供灵活高性能加速。

Patrick Dorsey先生首先对Stratix 10 DX做了详细的介绍:“UPI为Compute Express Link(CXL)路线图提供了新路径。正因为Stratix 10 DX支持UPI,因此它的一个关键价值就是能够扩展系统内存。搭配英特尔至强处理器,这种扩展是惊人的,因为我们支持8个独立的傲腾™DC持久内存控制器,总容量可到4TB。”

Stratix 10 DX FPGA向客户以及市场提供解决方案的主要领域包括这三个方面:低时延;高带宽;对于基础设施与应用的加速。

在至强可扩展处理器的基础上,通过应用Stratix 10 FPGA,使处理器和FPGA进行非常高效的合作,这是因为它们使用的是UPI以及符合PCIe Gen4的协议。符合UPI一致性的好处体现在,大部分的内存,无论是DDR还是傲腾,通过这种方式在至强处理器与FPGA之间共享存储,在共享过程中不用进行数据迁移或者数据拷贝。这就是一致性和UPI带来的根本性好处,因为数据迁移和拷贝会带来高成本,同时也会降低系统的性能。

接下来,Patrick Dorsey先生通过一些参数,展示了Stratix 10 DX和以往普通FPGA相比的提速证明:“在边缘计算应用,例如AI或者是神经网络的计算任务上。Stratix 10 DX拥有UPI之后,对比仅仅使用PCIe的响应速度快37%。而在网络应用当中,拥有了PCIe Gen4之后,是前一代PCIe Gen3带宽的两倍,这使得数据处理更为快速,同时也拥有以太网功能,这也是FPGA所带来的。第三则是在数据中心,云服务提供商或是企业级数据中心方面,通过英特尔的异构计算架构,至强可扩展处理器再加上FPGA,也就是多节点的计算架构,同时拥有PCIe Gen4与UPI的互联,总带宽是过去的2.6倍。”

总结起来,新品有以下独特之处:与之前的FPGA型号相比,英特尔认为Stratix 10 DX FPGA提供了新功能和接口特性,其中包括:

· 与特定的英特尔至强可扩展处理器组合,UPI接口可将延迟降低37% ,并通过一致的数据移动和28GB/秒的理论峰值传输速率而提高整个系统的性能。我们预计将在2021年提供超高速协议(Compute Express Link),具有内存一致性的FPGA接口是英特尔路线图的一部分。

· 符合PCI-SIG标准的Gen4 x16接口提供32GB/秒的理论峰值数据带宽。数据中心和非数据中心应用的吞吐量大约将提高1倍以上。

· 内存控制器支持每个FPGA8个独立的傲腾™DC持久内存控制器,总容量可到4TB。

· Stratix 10 FPGA的其他现有功能还包括:100GB/秒的以太网,HBM2内存堆栈和带外设的四核ARM Cortex-A53处理器子系统。

与VMware深入合作

从6月开始,英特尔就已经出货工程级样品设备与开发套件给全球客户,其中也包括中国客户。对于这些早期的技术采纳客户,除了提供硬件设备之外,英特尔还向他们提供全套开发工具以及API。

在最近几次英特尔FPGA产品宣布过程中,并不仅仅是公布产品,同时还会宣布和合作伙伴的进展。而这一次宣布的合作伙伴是VMware,与VMware的合作也是英特尔市场进入策略中很重要的一部分。

为此,Patrick Dorsey先生特别强调道:“VMware和英特尔之间有着非常重要的合作,VMware使用英特尔Stratix 10 DX来加速其应用解决方案的开发。目前我们合作的具体细节还没有公布,但是很快我们就会宣布这方面的合作。通过使用英特尔UPI以及缓存一致性的能力,能够极大地加速了VMware应用解决方案的开发过程。”

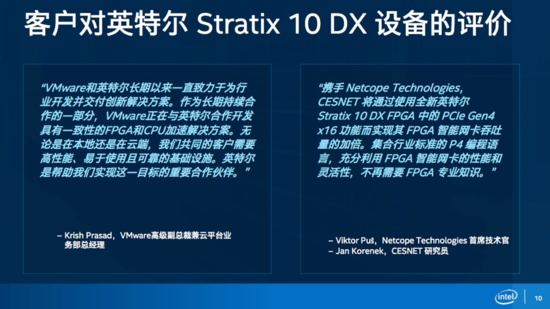

除此之外,我们还看到英特尔的一些合作伙伴对于Stratix 10 DX的评价。

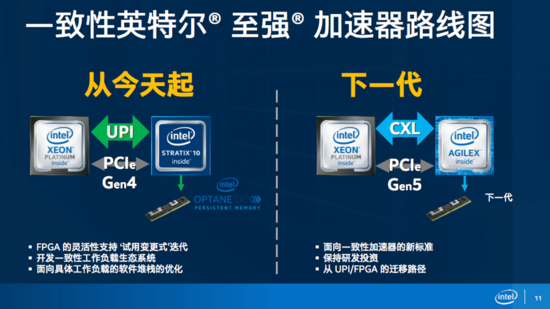

UPI向CLX无缝升级

对于未来的完整产品路线图,Patrick Dorsey先生表示Stratix 10 DX FPGA只是一个开始。“英特尔将会推出Agilex,也就是基于10纳米制程的英特尔的FPGA。它将支持下一代UPI,也就是基于CXL的开放标准接口。同时它将会支持下一代PCIe标准。最重要的是,现在应用开发者、系统集成商以及各类设计人员就已经可以使用UPI去进行应用开发。在Agilex推出之后我们将帮助客户进行向CLX进行无缝转移,以及后续的迭代过程。因此客户可以持续的享受带宽提升和时延降低的好处。”

未来是异构的时代,AI芯片、CPU、GPU、FPGA,英特尔是业界唯一一个囊括所有架构的厂商。但是,仅仅拥有四种架构是不够的,要保证客户能够充分利用这些架构的优势。因此,英特尔通过两个方面来实现这些架构的融合,以便更好的服务客户。第一是针对开发者,第二是针对端到端的硬件部署。相信未来随着产品性能的提升、解决方案更加丰富和融合,英特尔在数据中心方面的优势将更加凸显。

史海拾趣

|

启动代码中堆栈的初始化是不是只是定义一下要用到的堆的长度,比如IRQ中断,按书上说堆空间是要自己申请的,而栈是系统自动分配的,要是这样的话那初始化就应该是只对堆的长度进行定义了?还有就是我怎么确定要定义多长的堆栈空间呢?谢谢了!… 查看全部问答> |

|

大家帮我看看,我用厂家提供的BSP生成的OS 在开发板上无法启动,有详细信息,该如何修改 下面的情况均在厂家提供的开发板上试验 内存情况: 内存:64MByte SDRAM(2片16位的SDRAM芯片组成32位接口) NOR Flash:32MByte内存(2片intel E28F128组成32位接口) 测试的BSP有下面两个 ...… 查看全部问答> |

|

请问“要通过中断来实时接收100ms的数据”,这个机制怎么建立阿 我最近想做一个红外码学习器,在按下遥控按钮后,就把接收到的红外数据保存下来。但是,在多进程里面由于有调度问题,实时性很难控制,不知哪位高手做过没有,请帮忙指点一下阿… 查看全部问答> |

|

快过年了,希望eeworld能组织个TI DSP开发板的团购! 快过年了,还有点余钱,希望eeworld能组织个TI DSP开发板的团购,这样在假期中能够边玩边学,两不误。 希望有相同想法的同学们顶起!!!!!!!!!!… 查看全部问答> |

|

通过使用MSP430G2452微控制器的LaunchPad Value Line开发包实现基于心电图的心率监测 这是一个基于Launchpad的心率监测评估工程,资料非常详细,包括原理图,光绘文件,BOM表,源码,说明文档(中文)。 好好享受吧! … 查看全部问答> |