历史上的今天

今天是:2024年12月05日(星期四)

2019年12月05日 | AVR+FPGA实现六路闭环电流控制程序

2019-12-05 来源:elecfans

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity XTKZQ is

port(

rst,clk : in std_logic; --时钟和复位信号,复位信号由AVR初始化手动给出

--avr 读写相关信号线

ale,rd,wr : in std_logic; --地址锁存、读、写信号

ad : inout std_logic_vector(7 downto 0); --地址数据复用信号线

--LED指示灯

led1,led2 : out std_logic;

--pwm

pwm1,pwm2,pwm3,pwm4,pwm5,pwm6 : out std_logic;

--ad8364信号线

adc_d: in std_logic_vector(15 downto 0);

adc_a0,adc_a1,adc_a2: out std_logic;

adc_reset: out std_logic;

adc_cs: out std_logic;

adc_wr: out std_logic;

adc_rd: out std_logic;

adc_holda,adc_holdb,adc_holdc: out std_logic;

adc_eoc: in std_logic;

adcclk_out: out std_logic;

--放大增益控制,此处每一路AD设置了两级放大增益

sw11: out std_logic;--控制模拟开关,调节放大增益

sw12: out std_logic;

sw21: out std_logic;

sw22: out std_logic;

sw31: out std_logic;

sw32: out std_logic;

sw41: out std_logic;

sw42: out std_logic;

sw51: out std_logic;

sw52: out std_logic;

sw61: out std_logic;

sw62: out std_logic

);

end XTKZQ;

architecture art of XTKZQ is

------------------------------------------------全局信号定义-------------------------------------------------------------------

--avr访问操作相关信号

signal adr : std_logic_vector(7 downto 0); --地址寄存器

signal data_buf : std_logic_vector(7 downto 0);

signal data_outctl : std_logic;

--pwm控制部分有三组变量,第一组是由avr写入,控制相应的占空比,这个是供调试使用

--第二组是自动pid控制使用的

--第三组是pwm计数使用的,根据pid_sw开关的设置决定读入第一组还是第二组的值

--pwm部分相关寄存器定义 寄存器暂时定义为8位

signal pwmfreq_reg : std_logic_vector(7 downto 0);

signal pwmocr1_reg : std_logic_vector(7 downto 0);

signal pwmocr2_reg : std_logic_vector(7 downto 0);

signal pwmocr3_reg : std_logic_vector(7 downto 0);

signal pwmocr4_reg : std_logic_vector(7 downto 0);

signal pwmocr5_reg : std_logic_vector(7 downto 0);

signal pwmocr6_reg : std_logic_vector(7 downto 0);

--pwm部分PID调节中用到的相关变量

signal pwmfreq_pid : std_logic_vector(7 downto 0);

signal pwmocr1_pid : std_logic_vector(7 downto 0);

signal pwmocr2_pid : std_logic_vector(7 downto 0);

signal pwmocr3_pid : std_logic_vector(7 downto 0);

signal pwmocr4_pid : std_logic_vector(7 downto 0);

signal pwmocr5_pid : std_logic_vector(7 downto 0);

signal pwmocr6_pid : std_logic_vector(7 downto 0);

--PWM计数用到的相关变量,这里定义为8位

signal pwm_cnt : std_logic_vector(7 downto 0);

signal pwmfreq : std_logic_vector(7 downto 0);

signal pwmocr1 : std_logic_vector(7 downto 0);

signal pwmocr2 : std_logic_vector(7 downto 0);

signal pwmocr3 : std_logic_vector(7 downto 0);

signal pwmocr4 : std_logic_vector(7 downto 0);

signal pwmocr5 : std_logic_vector(7 downto 0);

signal pwmocr6 : std_logic_vector(7 downto 0);

--自动闭环控制相关寄存器定义

signal pid_sw : std_logic_vector(7 downto 0); --闭环控制开关,此寄存器为0x01时开启自动闭环控制

--六个AD寄存器位,用于存放设定的AD值

signal adcset1h_reg,adcset1l_reg,adcset2h_reg,adcset2l_reg : std_logic_vector(7 downto 0);

signal adcset3h_reg,adcset3l_reg,adcset4h_reg,adcset4l_reg : std_logic_vector(7 downto 0);

signal adcset5h_reg,adcset5l_reg,adcset6h_reg,adcset6l_reg : std_logic_vector(7 downto 0);

--时钟分频相关变量

signal clkcnt : std_logic_vector(16 downto 0);

signal adc_clk : std_logic; --adc时钟信号

signal pwm_clk : std_logic; --pwm时钟信号

signal pid_clk : std_logic; --pid时钟信号,用于调节pid的反应速度

--led指示相关变量

signal led_clk : std_logic; --led时钟信

signal led1_cnt : std_logic_vector(7 downto 0);

signal led2_cnt : std_logic_vector(7 downto 0);

signal led1s : std_logic;

signal led2s : std_logic;

--ads8364信号

signal adcdata1h_reg,adcdata1l_reg,adcdata2h_reg,adcdata2l_reg : std_logic_vector(7 downto 0);

signal adcdata3h_reg,adcdata3l_reg,adcdata4h_reg,adcdata4l_reg : std_logic_vector(7 downto 0);

signal adcdata5h_reg,adcdata5l_reg,adcdata6h_reg,adcdata6l_reg : std_logic_vector(7 downto 0);

signal adc_data_buf : std_logic_vector(15 downto 0);

--定义读取过程的各个状态

--13位控制分别为 hold adc_a rd 状态机状态5位 hhhabcr

---------------------------------------------------98365

constant st0 :std_logic_vector(11 downto 0):="000000100000";--启动转换

constant st1 :std_logic_vector(11 downto 0):="111000100001";--进入17个周期等待转换结束,不检测EOC

constant st2 :std_logic_vector(11 downto 0):="111000100010";

constant st3 :std_logic_vector(11 downto 0):="111000100011";

constant st4 :std_logic_vector(11 downto 0):="111000100100";

constant st5 :std_logic_vector(11 downto 0):="111000100101";

constant st6 :std_logic_vector(11 downto 0):="111000100110";

constant st7 :std_logic_vector(11 downto 0):="111000100111";

constant st8 :std_logic_vector(11 downto 0):="111000101000";

constant st9 :std_logic_vector(11 downto 0):="111000101001";

constant st10 :std_logic_vector(11 downto 0):="111000101010";

constant st11 :std_logic_vector(11 downto 0):="111000101011";

constant st12 :std_logic_vector(11 downto 0):="111000101100";

constant st13 :std_logic_vector(11 downto 0):="111000101101";

constant st14 :std_logic_vector(11 downto 0):="111000101110";

constant st15 :std_logic_vector(11 downto 0):="111000101111";

constant st16 :std_logic_vector(11 downto 0):="111000110000";

constant st17 :std_logic_vector(11 downto 0):="111000110001";

constant st18 :std_logic_vector(11 downto 0):="111000110010";

constant st19 :std_logic_vector(11 downto 0):="111000010011";--读ch1数据

constant st20 :std_logic_vector(11 downto 0):="111001110100";

constant st21 :std_logic_vector(11 downto 0):="111001010101";--读ch2数据

constant st22 :std_logic_vector(11 downto 0):="111010110110";

constant st23 :std_logic_vector(11 downto 0):="111010010111";--读ch3数据

constant st24 :std_logic_vector(11 downto 0):="111011111000";

constant st25 :std_logic_vector(11 downto 0):="111011011001";--读ch4数据

constant st26 :std_logic_vector(11 downto 0):="111100111010";

constant st27 :std_logic_vector(11 downto 0):="111100011011";--读ch5数据

constant st28 :std_logic_vector(11 downto 0):="111101111100";

constant st29 :std_logic_vector(11 downto 0):="111101011101";--读ch6数据

史海拾趣

|

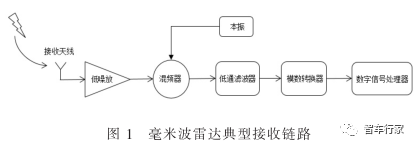

摘要:本应用笔记比较了集成RF混频器与无源混频器方案的整体性能,论述了两种方案的主要特征,并指出集成方案相对于无源方案的主要优点。 过去,RF研发人员在高性能接收器设计中使用无源下变频混频器取得了较好的整体线性指标和杂散指标。但在这 ...… 查看全部问答> |

|

Pause Trigger,它根据触发信号的电平来决定是否执行采集,也就是说可以在采集开始后暂停或继续采集. 可以在时钟属性中设置这种方式。一般需要采用外部时钟或计数器时钟。… 查看全部问答> |

|

vs2005开发环境,C#语言开发的pda程序怎么不能操作sqlce2.0数据库怎么办 我现在做的pda程序就是要操作sql ce2.0,但是用的vs2005和c#语言开发的程序好像不能操作它(能操作3.0)。 我现在数据库是不能动了,只能想办法来操作这个数据库,听说vs2003+c#是可以操作sql ce2.0数据库的,除了这 ...… 查看全部问答> |