历史上的今天

今天是:2025年08月09日(星期六)

2021年08月09日 | 1.3.2时序图分析示例

2021-08-09 来源:eefocus

以Nor Flash为例,分析一下2440和Nor Flash的通信时序。

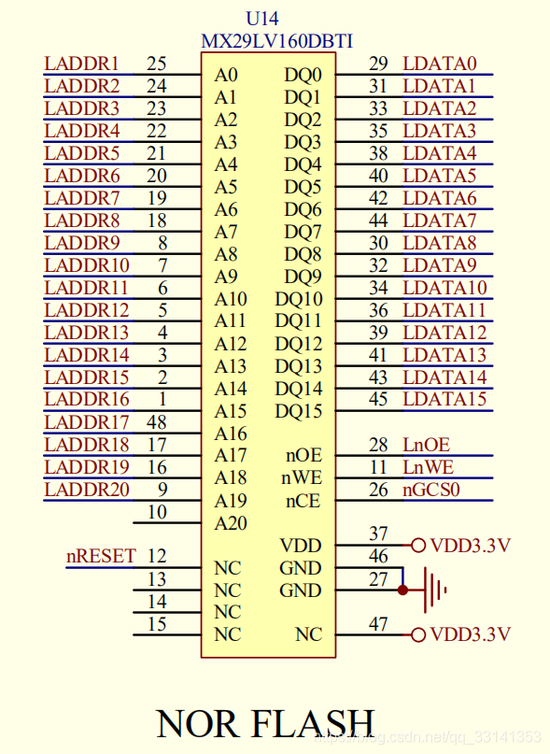

Nor Flash的电路图如上所示,与2440的大致连接如下图所示,有地址线Addr,数据线Data,片选信号nCS,读使能nOE,写使能nWE。

以2440芯片手册提供的读时序图为例,分析一下2440从存储芯片中读数据的时序。

从左到右分析时序图,可以看出,通讯开始时,2440最先发出地址信号,然后依次发出片选信号和读信号并读取数据,之后再将读信号,片选信号和地址信号释放掉。

对比Nor的芯片手册时序图,我们就可以知道上面的各个T值应该怎么设计。

根据对比我们可以确定,2440的Tacs对应Nor的Tacc,表示发出地址线后多久数据才有效,AC特性表中显示最大值为70ns,这是表示各个芯片的功能略有差异,但是最大不会超过0ns,所以我们将该值设为70ns即可。

然后是2440的Tcos,对应Nor的Tce,表示选中片选后多久数据才有效,同样为70ns。

片选选中后,还需要发出读使能信号Toe,这个信号在2440的时序图中没有标注,但是Nor的手册上是有的,最大为30ns。

当读出数据后,还需要将片选,读使能释放,从Nor的芯片手册可以看到,这里有一个Toh时间,表示在地址,片选,读使能释放之后数据的保持时间,最小为0。还有一个Tdf,表示在读使能和片选释放后,数据的浮动时间,在这段时间内,数据线没有回到高阻状态,所以数据是不稳定的,这段时间MCU不能访问其他芯片,否则有可能会出错,最大为30ns。(事实上这个Tdf并不需要关注,假设Tdf设为0,则在读完数据后立刻又操作芯片,这个时候还需要先将片选读使能这些信号发出并等待70ns,等70ns过去读数据时数据线早已回复正常状态)

最后,是Nor的Trc,表示读周期时间,就是读一次需要花费的时间,这个值对应2440的Tacc,最小设置为70ns。

所以,Nor的时序设置如下图所示。

为简单,我们可以可以设置同时发出片选信号CE#,读使能OE#和地址信号Address,然后设置Tacc为70ns。这样,片选,读使能和地址信号都会保持70ns可满足Nor的要求,同时也可以满足读周期。

刚刚上电时,我们程序还没跑,这个时候将使用默认值,根据2440的芯片手册,Tacc的默认值为111,即为最大值,外接存储器使用的是高速时钟总线HCLK(根据S3C2440的Block Diagram确定)这个时候HCLK时钟采用外接晶振,为12MHz,所以Tacc = 14 * HCLK 约等于 1166ns,足够任何控制器使用了。

上一篇:1.3.1不同位宽设备的连接

下一篇:1.3.3 SDRAM的设置

史海拾趣

|

新手请教verilog实现VGA显示移动小球的问题:使用ALTER公司的QuartusII软件开发,小弟现在想要实现一个用字模实现的小球,在屏幕上斜线移动的问题,但球会逐行显示又逐行消失,若只横向移动,则能一直显示,希望大家不吝赐教,部分代码如下: modu ...… 查看全部问答> |

|

根据时序要求,我们设定VM/VDEN信号作LCD的ENAB信号,VCLK信号作LCD的NCLK信号。要想得到合适的VM和VCLK波形,就要正确设定寄存器的值,根据寄存器的值与VM和VCLK波形的关系,我们设定了如下关键寄存器的值: HSPW=10;HBPD=100;HFPD=47; VSPW=1;VBPD=37 ...… 查看全部问答> |

|

1PG的#18#17位置设置(1)的设置范围是“0到正负999999”,如果我的伺服驱动器设定每转输入100000个脉冲,那么我能让电机旋转的圈数最多只有9圈多?比如我要电机转15圈,那么每转脉冲数乘以旋转圈数(100000*15=1500000)就超出了设定范围了!如果 ...… 查看全部问答> |

|

一、做个电子负载 板子早就打好了,这10块板一直在睡着,没有动 这次准备使用C2000 LaunchPad把它做起来。 二、做个数字电源 原来使用F28035做的BUCK部分,性能不错。这次使用F28027来做,只做BUCK型降压的电源。 PCB还没有做,或者使用试 ...… 查看全部问答> |

|

EPwm1Regs.TBPRD = 5000; EPwm1Regs.TBPHS.half.TBPHS = 0; EPwm1Regs.TBCTR = 0; EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; &n ...… 查看全部问答> |