历史上的今天

今天是:2024年10月22日(星期二)

2021年10月22日 | stm32专题十六:IIC(一)硬件结构框图

2021-10-22 来源:eefocus

STM32的I2C特性及架构:

1 硬件实现协议:

由STM32的I2C片上外设专门负责实现I2C通讯协议,只要配置好该外设,它就会自动根据协议要求产生通讯信号,收发数据并缓存起来,CPU只要检测该外设的状态和访问数据寄存器,就能完成数据收发。这种由硬件外设处理I2C协议的方式减轻了CPU的工作,且使软件设计更加简单。

stm32的硬件IIC,在某些情况下会出现错误,但也没有必要去纠结这个问题。

2 软件模拟协议:使用CPU直接控制通讯引脚的电平,产生出符合通讯协议标准的逻辑。

STM32的I2C外设可用作通讯的主机及从机,支持100Kbit/s和400Kbit/s的速率,支持7位、10位设备地址,支持DMA数据传输,并具有数据校验功能。

stm32硬件IIC的内部:

1 通讯引脚

IIC1

IIC2

![]()

2 时钟控制逻辑

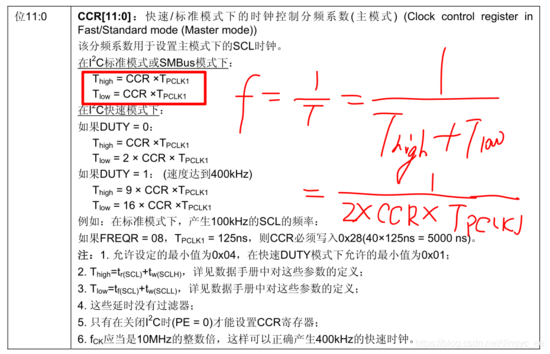

时钟控制逻辑,直接通过一些信号线与SCL引脚相连,通过这些硬件逻辑控制SCL线。时钟控制寄存器CCR,配置了SCL线的模式(标准模式100kHz,快速模式400kHz)、速度、占空比等参数,而实际上,标准库函数会帮我们计算好的,不需要每次都去手动计算。

这里计算分频系数,如何理解?

以标准模式为例,APB1总线的时钟信号PCLK1 = 36M,则T(PCLK1) = (1/36)ns,要产生100kHz的频率,则CCR必须写入的值为:2 * CCR * (1 / 36)ns = 100kHz,计算得到CCR = 180。

3 数据控制逻辑

连接到SDA引脚。

I2C的SDA信号主要连接到数据移位寄存器上,数据移位寄存器的数据来源及目标是数据寄存器(DR)、地址寄存器(OAR)、

PEC(帧校验)寄存器以及SDA数据线。

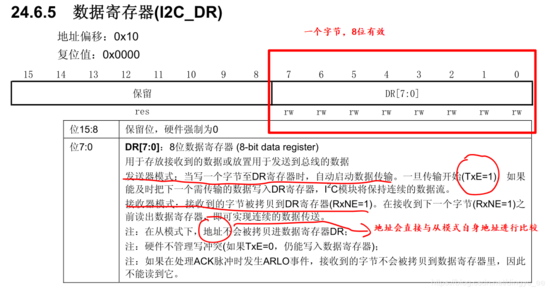

首先来看数据寄存器DR

当向外发送数据的时候,数据移位寄存器以“数据寄存器”为数据源,把数据一位一位地通过SDA信号线发送出去;

当从外部接收数据的时候,数据移位寄存器把SDA信号线采样到的数据一位一位地存储到“数据寄存器”中;

比较器的作用:IIC会有一个自身地址寄存器,用于作为从机。当作为从机时,必须要有IIC设备地址,通过软件配置可以写入到自身地址寄存器内。当主机寻址时,比较器会将地址比较,来确定主机是否在叫自己。

PEC寄存器:用于做数据校验,几乎不用。

4 整体控制逻辑

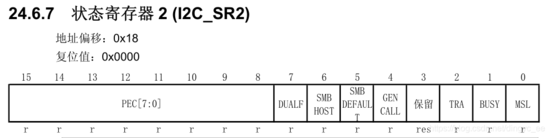

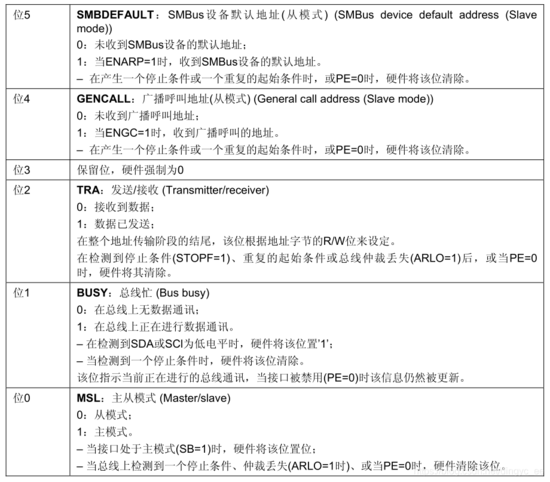

包含控制寄存器CR1 CR2和状态寄存器SR1 SR2。

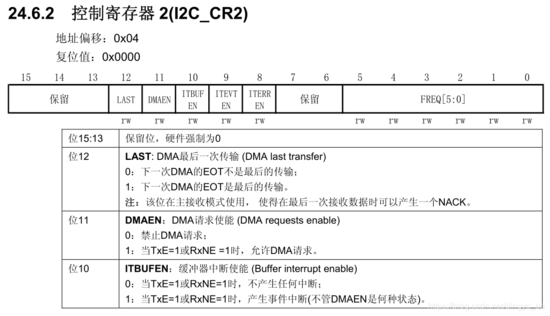

整体控制逻辑负责协调整个I2C外设,控制逻辑的工作模式根据我们配置的“控制寄存器(CR1/CR2)”的参数而改变。其中,CR1寄存器控制各种起始、结束的使能,CR2寄存器管理中断。

还有一个比较重要的地方:

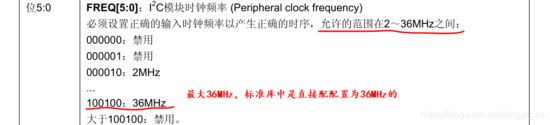

配置的是CR2寄存器的FREQ[5:0]位:

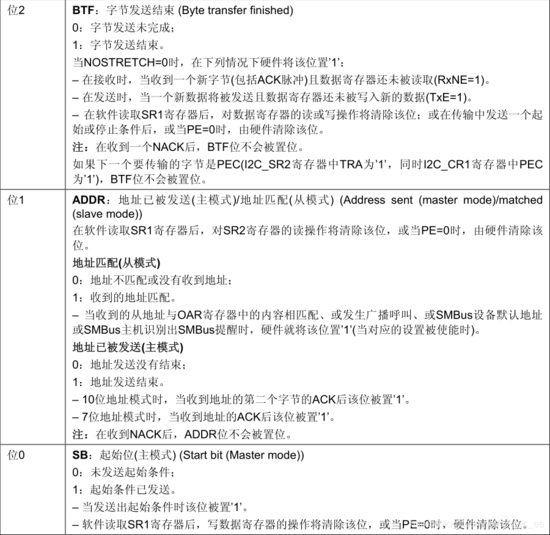

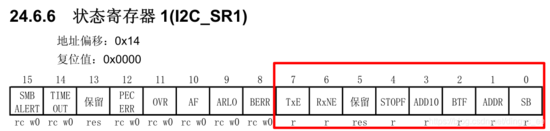

在外设工作时,控制逻辑会根据外设的工作状态修改“状态寄存器(SR1和SR2)”,只要读取这些寄存器相关的寄存器位,就可以了解I2C的工作状态,这个非常重要,我们编程时要参考这些标志位。接下来,详细的看一下每个标志位的意义。

这些标志位,对应了IIC的时序图种,产生的各种事件标志。

然后是状态寄存器CR2

史海拾趣

|

今天遇到一个奇怪的现象: 我做了两种不同的功放: 一个是LM386N搭建的电路(5V供电,单端输入,差分输出) 另一个是MAX9700搭建的电路(3.3V供电,单端输入,差分输出) 功放输入用相同的音源,音源芯片的电压等 ...… 查看全部问答> |

|

开始做一下自我介绍吧,我是一名湘潭大学05级自动化专业的学生。性格能内能外,觉得 还应该不断完美。下面说一说我大学前面三年的生活吧。 大一大二没学什么课外的知识,平平淡淡,如果参加社团不算的话。大三有机会能够跟一 个老 ...… 查看全部问答> |

|

本帖最后由 paulhyde 于 2014-9-15 09:34 编辑 大家可能都是新来的没钱,最近都是比较忙的。所以有的资料还是应该共享一下。以后可以慢慢来弄芯币,但是我觉得最近几天还是应该open一下。抛砖引玉!另外,我弄的大多是电源类的,所以其他方面的比 ...… 查看全部问答> |

|

已经搞定 问题的原因1:max232的电容用的是25V/1uf 的电解电容,应该用50V的 问题的原因1:但是买电脑不带串口,只是有串口的扩展插口,但是插口与正常的顺序不一样,按标准的改过来就可以了… 查看全部问答> |

|

引言 电源装置,无论是直流电源还是交流电源,都要使用由软磁磁芯制成的电子变压器(软磁电磁元件)。虽然,已经有不用软磁磁芯的空芯电子变压器和压电陶瓷变压器,但是,到现在为止,绝大多数的电源装置中的电子变压器,仍然使用软磁磁芯。因此 ...… 查看全部问答> |