历史上的今天

今天是:2024年11月10日(星期日)

2021年11月10日 | ATmega64 时钟系统及其分布

2021-11-10 来源:eefocus

时钟系统及其分布

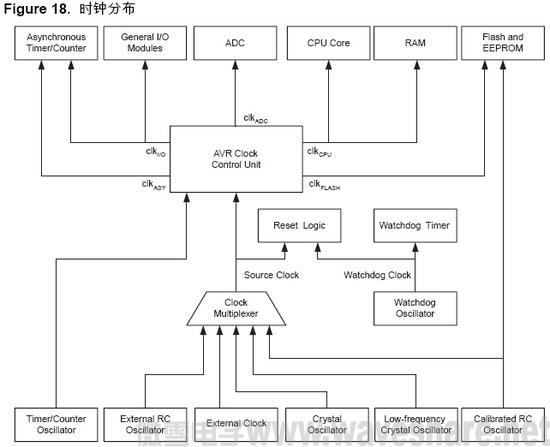

Figure 18为AVR的主要时钟系统及其分布。这些时钟并不需要同时工作。为了降低功耗, 可以通过使用不同的睡眠模式来禁止无需工作的模块的时钟,如 P42“ 电源管理及睡眠模 式” 所示。

CPU 时钟- clkCPU

CPU时钟与操作AVR内核的子系统相连,如通用工作寄存器文件、状态寄存器以及保存堆 栈指针的数据存储器。终止CPU 时钟将使内核停止工作和计算。

I/O 时钟- clkI/O

I/O时钟用于主要的I/O 模块,如定时器/ 计数器、SPI 和USART。I/O 时钟还用于外部中断 模块。但是有些外部中断由异步逻辑检测,因此即使I/O 时钟停止了这些中断仍然可以得 到监控。此外,TWI 模块的地址识别功能在没有clkI/O 的情况下也是异步实现的,使得这 个功能在任何睡眠模式下都可以正常工作。

Flash 时钟- clkFLASH

Flash 时钟控制Flash 接口的操作。此时钟通常与CPU 时钟是同步的。

异步定时器时钟- clkASY

异步定时器时钟允许异步定时器/ 计数器直接由外部32 kHz 时钟晶体驱动,使得此定时 器/ 计数器即使在睡眠模式下仍然可以为系统提供一个实时时钟。

ADC 时钟- clkADC

ADC具有专门的时钟。这样可以在ADC工作的时候停止CPU和I/O时钟以降低数字电路产 生的噪声,从而提高ADC 转换精度。

上一篇:ATmega64 时钟源

下一篇:ATmega64 外部存储器接口

史海拾趣

|

大家好,我在进行MC55的测试中遇到一个问题有疑惑,问题是这样的: 我需要下位机通过GPRS无线网络传输数据包给上位机,而且我需要三个数据包连续发送给上位机,比如每一包数据大小为800字节, ...… 查看全部问答> |

|

思科中国研发中心(CRDC)需要招聘Cable STB senior software Developer 2名,tester 1名,field engineer 1名。这是一个新成立的部门,因为目前经济形势不好,在hiring freeze的大形势下,还批下了4个职位。这4个人招进来之后,会作为新部门的key pe ...… 查看全部问答> |

|

各位大侠,请教: 8255或8155的三个I/O口PA,PB,PC的各个I/O口可以任意设定输入输出方式嘛?例如,可以设定PA0为输入,而PA1为输出嘛?… 查看全部问答> |

|

本人是计算机专业毕业,工作通信行业FPGA。目前工作使用的芯片是Xinlinx ISE,语言是verilog。 由于以前的专业和现在工作不怎么对口,FPGA的基础几乎没有。相关的就只学过数电,什么信号系统、数字信号处理、软件无线电都没学过。而且以前数电、微 ...… 查看全部问答> |

|

所有的STM32芯片都内置了一个硬件的CRC计算模块,可以很方便地应用到需要进行通信的程序中,这个CRC计算模块使用常见的、在以太网中使用的计算多项式:X32 + X26 + X23 + X22 + X16 + X12 + X11 + X10 +X8 + X7 + X5 + X4 + X2 + X + 1写成16进 ...… 查看全部问答> |