历史上的今天

今天是:2024年12月10日(星期二)

2021年12月10日 | 三星卧薪尝胆 2nm工艺4年后量产:和IBM 2nm不同

2021-12-10 来源:快科技2018

在先进半导体工艺上,台积电目前是无可争议的老大,Q3季度占据全然53%的晶圆代工份额,三星位列第二,但份额只有台积电的1/3,所以三星押注了下一代工艺,包括3nm及未来的2nm工艺。

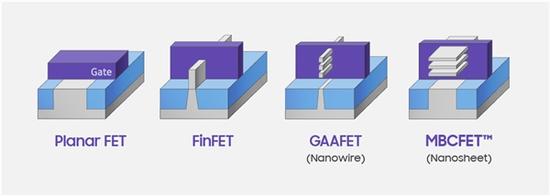

根据三星的计划,3nm工艺会放弃FinFET晶体管技术,转向GAA环绕栅极,3nm工艺上分为两个版本,其中3GAE(低功耗版)将在2022年年初投入量产,3GAP(高性能版)则会在2023年年初批量生产。

对比5nm,三星新的3nm GAA可以让面积缩小35%,同功耗下性能提高30%,同性能下功耗降低50%。

再往后就是2nm工艺,三星高管日前再次表态2nm工艺会在2025年量产。

不过具体的工艺指标还没公布,只知道还是GAA晶体管,跟3nm一样基于MBCFET(多桥沟道FET)技术,这是一种纳米片晶体管,可以垂直堆叠,而且兼容现在的CMOS工艺,共享设备与制造方法,降低了新技术的升级成本。

三星的2nm工艺是一大进步,创新亮点不少,而且跟现在已有的2nm技术不同——此前IBM全球首发了2nm芯片,指甲盖大小的面积就可以集成500亿晶体管,相比7nm工艺提升了45%的性能或者减少75%的功耗,预计2024年量产。

三星也参与了IBM的2nm技术,然而自己量产的2nm技术跟IBM的2nm并不一样,后者需要新的生产方法,三星还会依赖自家研发的2nm技术。

史海拾趣

|

请教高手电路图中的难点D13,D41,D42三个二极管再电路中是什么用处? 如果LM324的1脚输出增加,那么D13,D41,D42三个二极管输出全部拉低,这对电路整体有什么影响呢?… 查看全部问答> |

|

IIC驱动中的结构如下: typedef struct _I2C_IO_DESC { DWORD SlaveAddr; // Target Slave Address UCHAR WordAddr; // Starting Sla ...… 查看全部问答> |

|

求用C语言写一个stm8s105输出2KHz的方波的程序。 刚接触STM8单片机,不知从何入手,希望有STM8单片机经验的人提供点建议。非常感谢!… 查看全部问答> |

|

一个项目计划使用AD9364这个器件,在阅读文档时候发现文档说明中,模拟地和数字地直接相连?神马个情况? Analog Ground. Tie these pins directly to the VSSD digital ground on the printed circuit board (one ground plane). … 查看全部问答> |