DFM方案的统合性和成本问题

2007-09-21 来源:电子工程专辑

从2007年DAC(Design Automation Conference)展会上的信息了解到,DFM(Design For Manufacturing)仍然是一个及其重要而引人注目的话题。但是在DFM的世界里”没有标准的数据形式”始终是一个遗留的问题。

随着90nm深亚微米技术的普及, 系统的变异导致了巨大破坏以及电特性失效。 这意味着硅材料已经不再遵循所设计的模型和理想的布局。结果需要在各个设计的阶段采用非常大的余量,很长时间的闭合周期, 长久的制造效果时间, 破坏影响及参数变化导致成品率损失的主要瓶颈在于如何正确地遵循DFM模型。

尽管在制造期间已经采用了工艺设备等改进的技术,但是仍旧有残余的可变性因素。 当模型是正确的时候这些系统的变异取决于布局形状并可得到正确的预测。 这些变异可以通过对晶体管门的关键维度和互联导线形状的测试得到预言。

DFM的目的是,在预先考虑制造上的问题后进行IC设计,从而迅速且准确地得到最高成品率。但是制造和设计之间相互交流的数据却根据EDA厂商和制造商的不同而不同。其次,因为IC本身也变得非常地复杂,实施DFM需要花费大量的成本和时间。因此确保各相关DFM厂商之间的整合性将毫无疑问成为主要的目标。

台湾的TSMC公司使用统一的独自开发的数据形式, 并且明确表示该公司的数据形式在TSMC内部虽然有效, 即便将此数据形式流用到其它公司之后也不能得到和该公司相同的结果。因为TSMC公司的制程数据是该公司独一无二的。所以TSMC公司里制造出来的掩模版是不可以在其它制造公司里使用的。

美国的很多设计工程师都认为目前所需要的完整统一的DFM工具却还不存在, 如果不谈所使用的工具和数据的话,设计制程里加上DFM工序的话,最低也要化上300万美元的设备费用。 这个金额对于新兴公司来说不是非需要不可的。因此成本问题也是一个很重要的课题。

我们认识到目前DFM市场的真实现状,认为”虽然TSMC在2006年6月举行的[TSMC DFM Compliant]上推出采用DFU制程, 既导入DFM模型的手法, 而且迄今为止似乎已经被认为最有效的DFM解决方案。 但是即便如此, 所推出的TSMC各种制程的DFM模型也没有办法在其它公司运用后得到同样的DFM效果, 而采用硬件DFM处理的话,其成本太高而且半导体设备升级的费用是非常之昂贵的,但是如果采用软件DFM处理, 无论制程如何提高,其升级将会是非常容易而且成本是最低的”。 同时”目前市场上出现的DFM检查规则工具很多是根据主要的制造商比如TSMC的制程规则制定的, 这种工具很难适用于其它制造商的制程, 因此设计公司反而会得到相反的效果。” ”所谓DFM缺陷是由半导体固有缺陷和制程缺陷所造成的,而直接影响制造的制程缺陷都会在布局中体现出来。半导体的固有缺陷在软件上采用统计算法很容易克服,但是制程中的缺陷就不是很容易提取出来了。”英国Predictions Software公司采用其独特发明的采样专利技术,使得制程中的各种缺陷非常容易地提取并在布局数据中有效地得到消除,从而大大提高了成品率,在根本上解决了DFM的问题。

Predictions Software公司的成品率提高工具包括有EYE, 这是IC成品率预言工具;PEYE-CAA, 这是关键区域分析工具;PEYE,则是布局分析修正以提高成品率工具。这三个配套工具都是工作于标准的布局GDSII文件。

EYE通过抽取样本来分析所设计的GDSII布局文件,因为EYE采用了Predictions Software公司独一无二的高精度的布尔采样专利技术,因此,如果芯片制造商提供的工艺技术缺陷数据是准确的话,那么测试出的IC成品率精度偏差将小于+/-1%。 测试出的结果报告可以使用HTML或EXCEL来显示。 同时,因为EYE可以自然地镶嵌在布局编辑器软件中,比如CADENCE公司的布局Virtuoso编辑器。这样就更加方便地在布局的时候进行成品率测试估算,以便尽力提高到期望IC成品率。

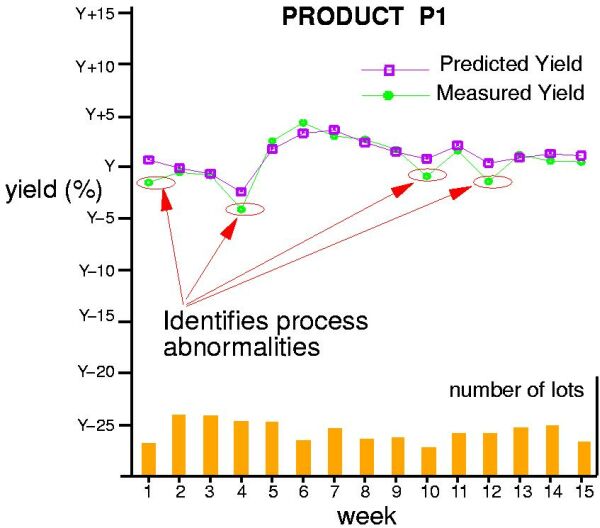

下图是ST公司公开的测试结果:

Inline yield prediction ST, Crolles.

下面是测试出的布局成品率地图:

这张布局成品率地图的具体成品率数值可以非常容易地输出到HTML或EXCEL文件格式中去。

PEYE-CAA是关键区域分析工具,它可以和CADENCE公司著名的布局编辑工具合为一体,在布局文件GDSII中找到缺陷之后可以迅速地使用布局编辑器进行修正。 那么什么是所说的缺陷呢?缺陷主要是指工艺技术缺陷类型,包括有:随即缺陷,系统缺陷,参数缺陷,用户工艺技术特定缺陷。而这些缺陷类型又有很多种类的具体缺陷,这里就不一一介绍了。那么关键区域又是什么呢?关键区域是在电特性上非常容易发展成为缺陷的活性瑕疵。

下面是镶嵌在CADENCE的布局编辑器Virtuoso里面的EYE结果表现图和输出结果图的比较。

下图所示的是缺陷修补的图示。

PEYE: Extra via added to layout

下图所示的是缺陷消除以及成品率提高前后的布局对比图。

这三个IC成品率提高工具组合套件可以相互交替使用。在具体处理缺陷的时候,客户可以使用脚本语言进行自动快速处理布局文件,从而可以根本上消除掉芯片中的缺陷使得客户的芯片得到最理想的成品率。

上面介绍了Predictions Software公司的EYE/PEYE-CAA/PEYE三个成品率提高工具的基本原理和最主要的功能, 该公司的主要技术是基于DFM要求进行布局数据的优化来提高成品率。根据目前的归类法它们应该属于DFM类工具。

Predictions Software公司的基于布局优化的DFM三套件是目前市场上最有效而成本最低的成品率提高工具。虽然半导体制造商理因可以提取出本公司各种工艺技术中的缺陷模型,但是由于中国的半导体制造商对于目前最先进的半导体生产设备特性和使用技巧的了解还十分有限, 加上针对半导体设备所使用的技术工艺库的改进办法也不甚了解。所以非常需要通过借助于国际上先进的EDA公司提炼出来的DFM工具技术和制程缺陷提取技术来帮助提高成品率。只有这样才可以或有潜力和其他半导体制造商竞争。值得注意的是,布局文件GDSII的成品率优化技术是DFM的最有效手段。Predictions Software公司的客户英飞凌公司说 “对一种典型的半导体产品来说,成品率提高1.7%的结果可以终身节约成本2.68兆美元 ”。 因此,无论是半导体制造商还是IC设计公司, Predictions Software的EYE/EYE-CAA/PEYE是最为推崇的成品率提高工具。

- 优傲机器人全面升级售后体系,推出专为中国市场量身打造的本土化服务

- CAN SIC知多少——新一代车载网络协议你用了没?

- 相约上海世博,与imc/GRAS/AP共赴汽车测试及质量监控博览会

- 清华“太极-Ⅱ”光芯片面世:成果登 Nature,首创全前向智能光计算训练架构

- Lattice半导体2024年第三季度财报:将裁员14%

- 陕西光电子先导院完成数亿元B轮融资

- NXP全新i.MX RT700跨界MCU搭载eIQ Neutron NPU, 以高性能、低功耗赋能AI边缘

- 庆祝在华四十周年 应用材料中国公司举办总部庆典仪式

- 美国FCC提议AI生成电话语音必须“自报”AI身份,以打击骚扰、欺诈信息

- 东芝推出具有低导通电阻和高可靠性的适用于车载牵引逆变器的最新款1200 V SiC MOSFET