英特尔Brennan:可以简单地把UCIe想象成芯片级的PCIe

2022-05-12 来源:EEWORLD

英特尔日前在On产业创新峰会上分享了有关新互连UCIe的更多细节,这是该公司长期计划的基础,即 x86、Arm 和 RISC-V 架构在单芯片封装中实现共存。

这家半导体公司正在采用模块化方法进行芯片设计,客户可以选择将 CPU、GPU 和 AI 加速器等计算模块塞入单个芯片封装中。英特尔在 3 月份与其他九家公司建立了通用 Chiplet 互连快速标准,作为高带宽、低延迟的连接器,供这些计算块在芯片内部进行通信。

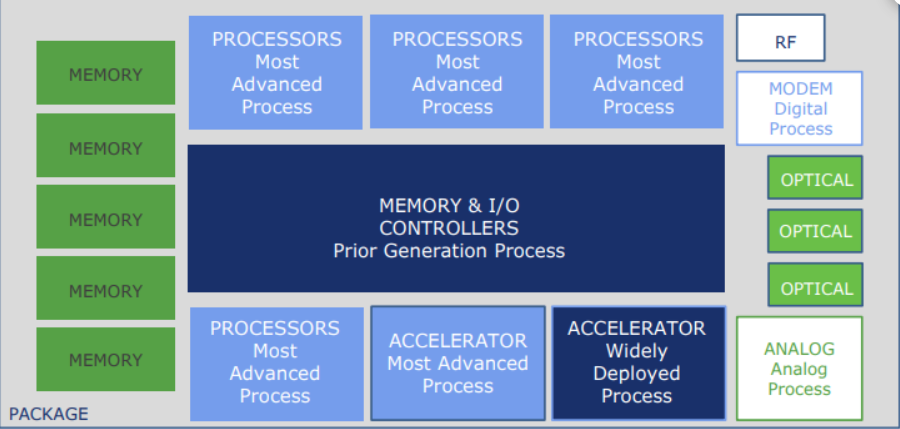

SOC封装级构建。混合和匹配来自多个来源和不同封装选项的模具。资料来源:UCIE 联盟

英特尔代工服务客户解决方案工程副总裁兼总经理 Bob Brennan 在周二的On产业创新峰会上表示:“如果你看一下带宽而不是功率,UCIe远远优于 PCI Express 之类的东西,”

Brennan 说,UCIe 的第一个版本将在相同距离和有限数量的通道上比 PCI-Express 快大约四倍。 Brennan 说,UCIe 有可能比 PCI Express 快 10 到 20 倍,通道之间的管道更多。

比较是相对于距离的。 Brennan 说,UCIe 设计用于芯片级基板上的极短距离,而 PCI Express 是在主板级实现的,其中数据传输距离更长,电气要求不同。

“可以将 UCIe 想象成 PCIe,但用于芯片。”Brennan 说。

UCIe 的创始成员包括 AMD、Arm、台积电、微软、高通和三星。英伟达当月晚些时候宣布将支持 UCIe 标准,但其名称仍未在 UCIe 网站上列出。

苹果不是 UCIe 的成员

“这是 UCIe 的第一个版本,我们与广泛的合作伙伴和我们的竞争对手组成的联盟将其推向市场。我很高兴看到大家很快就聚到了一起。”Brennan说。他没有提供规范何时发布的时间表。

英特尔正在开放其芯片,以便将其自主研发的 x86 内核与基于 Arm 或 RISC-V 架构的计算内核一起封装。例如,至强芯片可以与封装中的 RISC-V 或 Arm AI 加速器共存。 Brennan 将内核封装称为“chiplet 机箱”,计算块通过 UCIe总线而不是PCIe连接。

“小芯片机箱的概念是,我们将提供一个硅机箱壳,作为我们客户使用的参考设计,在概念上类似于我们进行电路板设计的方式。但这是芯片设计。”

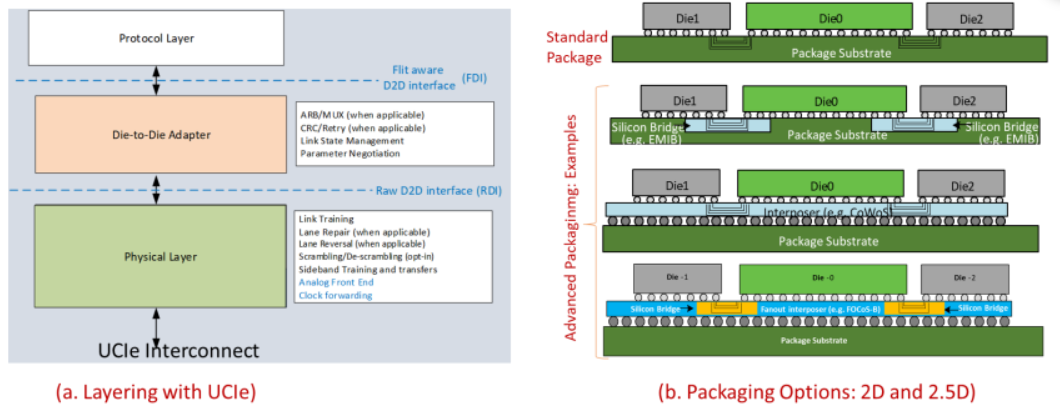

UCIe 支持的封装选项,包括英特尔的 EMIB(嵌入式多芯片互连桥)和台积电的 CoWoS(Chip-on-Wafer-on-Substrate)技术。

“未来我们必须照顾协议层。”Brennan说。

最初的支持是 CXL(Compute Express Link)协议,这是一种基于 PCIe 5.0 的行业标准,用于将 CPU 芯片封装连接到加速器、存储和内存组件。未来可能支持许多其他协议,包括 CHI(相干集线器接口),它是 ARM 支持的 AMBA(高级微控制器总线架构)的一部分。目标是增加映射到专有协议的能力,以及协议的向后兼容性,以便公司可以保护他们在软件方面的投资。

Brennan表示:“我们还计划在未来与联盟中的合作伙伴一起制定不同的形式因素、管理、安全性和许多许多事情。”

Brennan 分享了几个片上 UCIe 设计的示例。一种是带有 CPU 子系统的芯片封装,它通过 UCIe 与硬件加速器以及管理和安全模块连接,EMIB 封装用于将芯片连接到DDR5 内存和 PCIe 链路。

- 新思科技发布全球领先的40G UCIe IP,助力多芯片系统设计全面提速

- UCIe 1.1 小芯片 / 芯粒互连规范发布,增强汽车领域功能

- 芯和半导体成为首家加入UCIe产业联盟的国产EDA

- UCIe在解决Chiplet标准化方面具有划时代意义

- Innolink-国产首个物理层兼容UCIe标准的Chiplet解决方案

- 芯动科技发布国产首个物理层兼容UCIe标准的Chiplet解决方案

- 芯原股份加入UCIe产业联盟

- 芯原股份正式加入UCIe产业联盟

- 破除被Chiplet边缘化质疑 封装厂将是UCIe的中坚

- AMD 推出第二代 Versal Premium 系列:FPGA 行业首发支持 CXL 3.1 和 PCIe Gen 6

- ASML在2024 年投资者日会议上就市场机遇提供最新看法

- 消息称内存原厂考虑 HBM4 采用无助焊剂键合,进一步降低层间间隙

- 英特尔中国正式发布2023-2024企业社会责任报告

- 贸泽电子与Analog Devices联手推出新电子书

- AMD 推出第二代 Versal Premium 系列:FPGA 行业首发支持 CXL 3.1 和 PCIe Gen 6

- SEMI:2024Q3 全球硅晶圆出货面积同比增长 6.8%、环比增长 5.9%

- 台积电5nm和3nm供应达到"100%利用率" 显示其对市场的主导地位

- LG Display 成功开发出全球首款可扩展 50% 的可拉伸显示屏

- 英飞凌2024财年第四季度营收和利润均有增长; 2025财年市场疲软,预期有所降低