基于改进型二步索引算法OSD电路的FPGA

2007-10-31 来源:电子测量技术

0 引 言

OSD(on screen display),即在屏显示系统,是实现人机界面交互的基础,在视频处理SOC中作为重要功能模块有着广泛的应用。

基于SOC技术的模块化设计要求各功能模块尽可能小地占用电路资源,以满足芯片系统对资源使用和面积的控制。对于OSD功能模块而言,存储器资源为主要开销。因此,减少存储器资源的使用对降低OSD模块电路资源需求有着重要的意义。

OSD电路中,字符索引算法的选取直接决定了存储器资源的使用情况,因此采用更优化的字符索引算法可以达到降低存储器资源需求量的目的。作者在逐字符索引法的基础上,针对该算法的缺点,提出了二步索引法。在保证OSD功能完整的同时,大大地降低了系统对存储器资源的需求。

1 二步索引算法的原理及特点

1.1 字符索引算法原理

字符索引算法是将OSD菜单中所显示的字符按菜单显示顺序进行编码,并存储于存储器中,在读取字符点阵信息以显示菜单时通过读取编码信息来索引所需字符信息。设菜单中字符尺寸为C1×Ch(bit),菜单共显示m行字符,每行显示n个字符,字符编码Ni×j,并且存储器中一个地址所存储的数据(bit)大于C1。则读取菜单中第i行第j个字符时,首先通过索引得到存储器中相应字符的字符编码Ni×j,索引地址可通过公式(1)得出:

add_mi×j=addr_n0×0+(i-1)n+n-1 (1)

将读取出的字符编码Ni×j转换成相应字符点阵信息在存储器中存储空间的首地址。地址的转换可通过公式(2)计算得到:

addr_di×j=addr_d0×0+Ch×(Ni×j-1) (2)

式中:addr_u0×0和addr_d0×0分别是字符编码存储器和字符点阵信息存储器中首地址指针。根据Ch控制从字符点阵信息存储器中读出地址范围为addr_di×j到addr_di×j+Ch的数据即完成了对菜单中第i行第j个字符的点阵数据信息的读取。

逐字符索引算法下,将空格按字符看待并进行编码,菜单每行固定显示n个字符,字符长度小于n的菜单行由空格来补齐。由于采用定长的存储结构,所以字符索引电路原理简单且易于实现,只需要根据菜单字行符长数n就可以计算出相应行字符的首地址指针。但这种存储结构的缺点也很明显,就是对存储器的使用量较大。在该算法下,可以计算出在OSD所需要的使用的存储器量为:m×n×Ch,如图1(a)所示。存人其中的“空格”(图中编码为“28”)会占用相当一部分的存储器资源。在一些情况中,用于补充空缺而存储的“空格”所占用的存储空间甚至会比字符点阵信息的存储空间还要多,这是对存储器资源极大的浪费。

1.2 二步索引算法原理

如果只存储字符点阵信息而不存储‘空格’,显然对节省存储器资源将有着很大的帮助。为达到这样的设计目标,在逐字索引法的基础上,通过改进提出了二步索引算法。

设第k幅菜单中显示nk行字符,菜单第i行中显示li个字符。其中,nk存储于寄存器中,li存储在一段地址长度为nk的字符数信息存储器中。在二步索引算法下,通过读取字符数信息存储器中的数据以及根据nk限制读出的li数据个数,可以确定菜单中各行所显示的字符的个数。第k幅菜单中第i行第j个字符的编码信息在存储器中的地址指针可以根据公式(3)确定:

读出字符编码数据Ni×j,仍然通过公式(2)得到相应字符在点阵信息存储器中存储地址段的首地址指针,从而读出全部的字符点阵信息。完整的数据读取操作过程如图2所示。

在二步索引算法中,引入了行显示字符数li和菜单显示字符行数nk2个参数,通过nk首先索引菜单中第i行的显示字符数li,根据li控制索引该行第j个字符编号Ni×j。根据li可以知道每行显示的字符数,所以字符编码信息可以按行顺序紧密的存储,即每行存储的数据采用非定长的方式,如图1(b)所示。与图1(a)所示的逐字索引法存储器结构相比,二步索引法在对存储器资源的节省方面效果是显著的。

2 二步索引法OSD电路结构实现

2.1 字符索引电路实现

如图3所示,相比于逐字索引法的电路实现结构,二步索引法的电路实现结构中增加了字符行寄存器和用于存放行字符数信息的存储器。字符行寄存器中存人nk,根据字符行计数器所计数据与nk比较来控制从行字符数存储器中读出的数据数。读出的行字符数信息li再用以控制显示第i行菜单字符所需从字符编码存储器中读出的字符编码数据数。读出的字符编码Ni×j通过地址生成电路转换成相应字符的点阵信息在字符点阵ROM中存储地址段的首地址,从而在字符点阵ROM中索引出相应字符的点阵数据,如此反复,可实现对全部字符点阵数据的索引。

2.2 数据输出控制与层混合叠加电路实现

从字符点阵ROM中读取出的字符点阵信息经过点阵重组电路的处理后将按字符Cl×Ch顺序的点阵信息转换成按菜单行顺序的格式存入到输出缓存中。输出缓存中数据的存储顺序如图3所示。

输出缓存能够存储整幅菜单的显示信息,以使菜单生成和菜单输出显示2个过程相互独立,从而使得在显示菜单的同时,可进行新菜单内容的读入,保证菜单显示的连贯胜。输出缓存容量大小由包含显示信息最多的一幅菜单决定。

从输出缓存中读出的数据用于控制生成菜单字符层,在层选择电路中与菜单背景层和属性条层进行叠加处理后输出一幅完整的菜单。字符层、菜单背景层和属性条层相互独立,由层混合控制电路控制进行混合叠加处理,再将菜单与屏幕背景层进行叠加输出混合视频信号。层混合叠加电路的实现结构如图4所示。

3 OSD电路的FPGA实现及功能验证

设计在Xilinx公司的ISE6.3软件环境下,使用Verilog HDL硬件描述语言对其电路逻辑进行描述,并以Xilinx公司xc2v1500bg575-4型为核心芯片的FPGA仿真验证平台对其进行硬件实现及功能验证。FPGA验证平台架构如图5所示。

验证平台输入模拟视频信号,经SAA7111A芯片电路A/D采样转变为数字视频信号接入FPGA验证平台。经过视频处理电路去隔行、尺寸缩放等处理的视频信号在图象混合电路中与OSD菜单混合后输出经DS90C38芯片电路转为LVDS(低压差分信号)信号并驱动液晶屏显示结果。

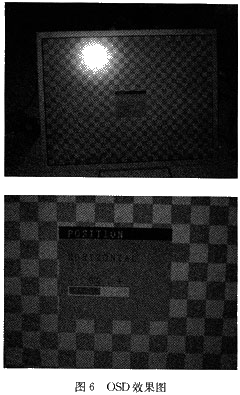

对2种字符索引算法下实现的OSD电路进行验证比较。OSD字符索引电路部分使用到的存储器资源可以分为字符编码存储器、行字符数存储器、字符行寄存器3种。以生成图6中所示菜单为例分析2种算法下OSD字符索引电路对存储器资源的使用情况,将结果列于表1中。

从表中可以看出,以二步索引算法实现的字符索引电路使用了8个bytes的行字符数存储器和1个byte的字符行寄存器,而以逐字索引算法实现的字符索引电路在这2类存储器上的使用量均为0。但是,后者在字符编码存储器的使用上却达到了96 bytes,远远多于前者50 bytes的使用量。从表1中可以看到,前者对存储器资源的总使用量比起后者减少了很大一部分。随着菜单尺寸的增加和显示的字符信息的增加,二次索引算法对存储器资源的节省效果也会更加的显著。

4 结束语

采用模块化设计方法实现的OSD电路,作为视频格式处理芯片的子电路模块,对硬件资源的使用将影响到整块芯片的电路性能。本文针对OSD电路中以存储器为硬件资源的主要开销这个特点,提出了采用二步索引算法实现的一种改进型字符索引结构的OSD电路。引入字符行寄存器和行字符数存储器,通过对行字符数和字符编码的二步索引,从而得到了菜单的显示信息,同时大大地降低了对存储器资源的使用。该算法的硬件结构简单,易于实现,在实现了同样的电路功能的前提下,大大节省了硬件资源的开销。

本文所介绍的基于二步索引算法实现的改进字符索引结构的OSD电路,将作为子模块电路集成于一款视频格式转换多媒体芯片的系统中,为其提供人机交互功能。该系统可应用于汽车电子、视频显示等多媒体处理场合。

- 美光亮相2024年进博会,持续深耕中国市场,引领可持续发展

- 高效环境感知:毫米波雷达数据采集、可视化及存储方案

- e络盟携手Flexxon,拓展先进工业级存储解决方案的全球分销网络

- keil中GD32 MCU IAP中APP的存储地址如何设置?

- 铠侠将开发新型 CXL 接口存储器:功耗、位密度优于 DRAM、读取快于 NAND

- GD32开发实战指南(基础篇) 第20章 GD32的存储结构

- 从富士通到RAMXEED,以全新一代FeRAM迎接边缘智能高可靠性无延迟数据存储需求

- 亿铸科技参与撰写,《中国存储器产业白皮书(2024)》发布!

- 如何有效减少自动驾驶中传感器数据的存储量

- 意法半导体推出Page EEPROM二合一存储器 提升智能边缘设备的性能和能效

- 祛魅固态电池:一文看懂这项大火的技术