历史上的今天

今天是:2024年11月18日(星期一)

2019年11月18日 | 揭秘英特尔显卡Ponte Vecchio:Xe架构,7nm制程

2019-11-18 来源: 超能网

Intel在SC19 HPC峰会正式开始前举办了一场“展前发布会”,会上Raja Koduri介绍了他们在HPC领域中的最新战略,更为重要的是,他揭晓了Intel新的,代号为"Ponte Vecchio"的计算用显卡,它基于Intel倾力打造的Xe架构。

图片来自于AnandTech

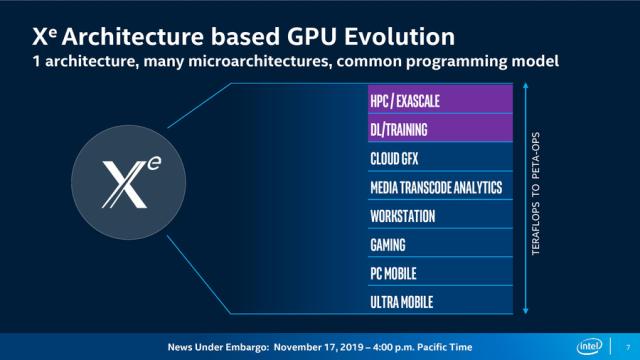

现在的GPU不仅仅是一个渲染计算机图形的处理器,它更是高性能计算领域的常客,Intel表示他们的Xe图形架构非常灵活,可以做到从低功耗领域到高性能计算领域的全覆盖:“一种架构,多种微架构,通用编程模型”,从图上我们也可以看出Intel在GPU领域中的野心非常大,未来Xe显卡架构也将覆盖他们几乎所有的产品线。

AnandTech

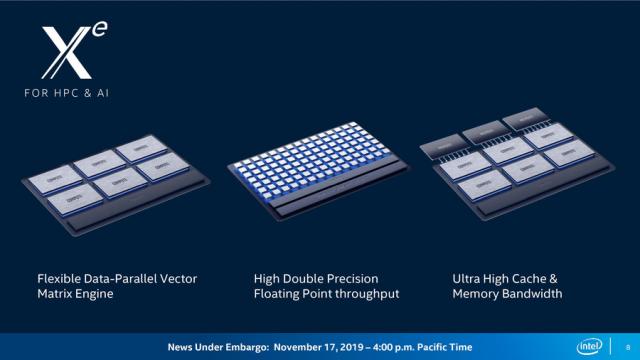

Xe架构的灵活性在于内部微架构的可定制性,或者说就是针对不同市场的关键应用推出相对应的架构,比如说在高性能计算市场上面推出具有高双精度浮点运算性能的产品,而针对AI加速市场可以在架构中塞入更多张量单元来进行针对性的加速。

AnandTech

上图指出了HPC版本的Xe架构将具有的三个特征,首先是针对AI领域的弹性数据并行向量矩阵引擎,它可以有效加速AI训练。第二个是双精度浮点单元,目前普通游戏图形对于双精度计算的需求并不高,不过在传统的高性能计算市场中,它仍然有着非常大的工作量,所以双精度计算单元仍然是高性能计算卡架构中的一个不可或缺的成员。最后是超高的缓存&内存带宽,对于计算卡来说这是帮助它实现高计算吞吐量的助推力量。

图片来自于Tom's Hardware

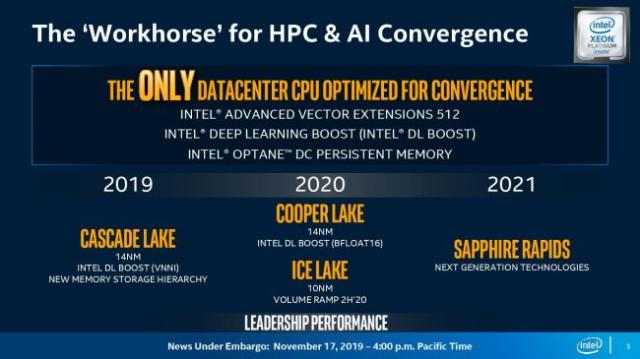

Ponte Vecchio是意大利佛罗伦萨阿诺河上面的一座著名的古桥(AC2故事线起始地),Intel使用了这座古桥的名字作为新的计算卡的代号,它将会使用Intel近年来研发的一系列新技术,比如7nm制程、Foveros 3D堆叠技术和EMIB片间互联技术,不过显卡要等到2021年才会正式登场。而最新基于PCIe 5.0的CXL互联技术可能在它的另一个分支,代号为"Sapphire Rapids"的数据中心级芯片身上亮相。

史海拾趣

|

本帖最后由 jameswangsynnex 于 2015-3-3 19:57 编辑 近年来,随着各种短距离无线通信技术的发展,人们提出了一个新的概念,即个人局域网PAN(Personal Area Network)。 PAN 核心思想是,用无线电或红外线或者蓝牙代替传统的有线电缆 ...… 查看全部问答> |

|

近日,天涯社区一名广州的网友“卖身找工作”,自称是仍然失业的应届毕业生,他结合眼下“被就业”“跨省追捕”等时兴话题及自 身的经历,以漫画“小强爬行记”道尽自己大学毕业以来就业路上的种种辛酸经历。他调侃自己为一只“踩不死的小强,就算 ...… 查看全部问答> |

|

在cmm文件中设置如下: &UBOOT_EXECUTED_ADDRESS=0x33e00000 &UBOOT_PATH=\"Y:\\svn\\uboot_tao\\uboot-1.3.4-m9\" &UBOOT_IMAGE=\"&UBOOT_PATH\\u-boot\" &UBOOT_CODE=\"&UBOOT_PATH\\\" print \"u-boot loading again for Debugging\" Data ...… 查看全部问答> |

|

= _T(\"searchlist.bat\"); //执行DOS命令 TCHAR szAppPath[MAX_PATH] = _T(\"\");& ...… 查看全部问答> |