历史上的今天

今天是:2024年09月24日(星期二)

2020年09月24日 | 通用输入输出口(GPIO)

2020-09-24 来源:eefocus

1概述

端口

I/O端口主要功能是用于内部单片机和外设进行通信的媒介。一个端口最多有8个引脚。

引脚

每个引脚都是独立的,也就是说当我们对其中一个引脚进行操作的时候不会影响到其他引脚。我们可以对引脚单独设置为数字输入或者数字输出。其中有些引脚还可以用着模拟输入和和外设中断。同一时刻只有一个功能映射到同一个引脚。

GPIO主要功能(我只列举我比较陌生的)

输入兼容5v电压

I/O口工作电压范围为1.6V到Vddiomax

I/O口的配置和使用

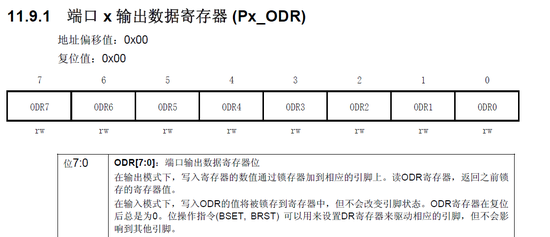

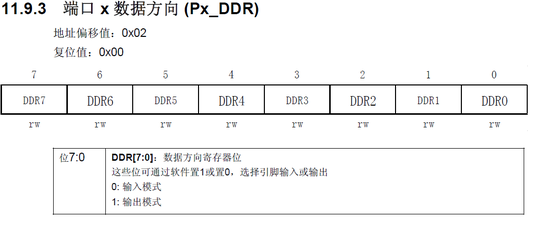

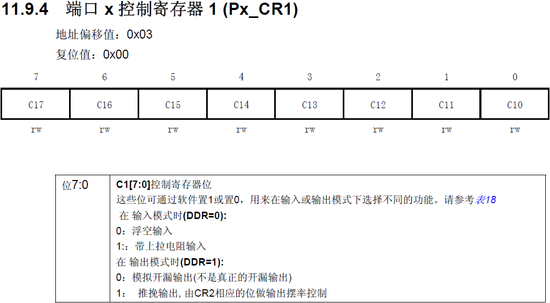

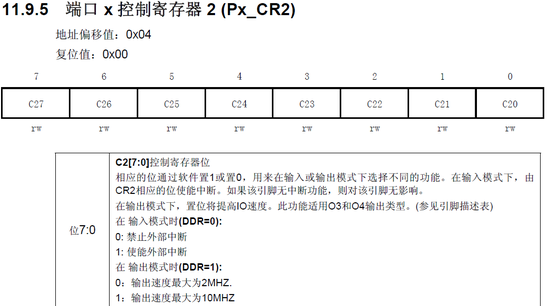

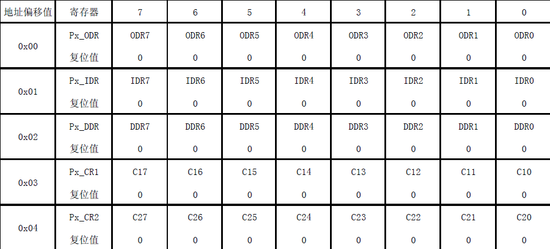

IO口常用的寄存器有5个ODR IDR DDR CR1 CR2

数据输出寄存器ODR 输入寄存器IDR 和方向寄存器DDR 控制寄存器1CR1 控制寄存器2CR2

需要注意的是这里的引脚位和寄存器的位是一一对应的,即寄存器中的位n对应于口的引脚n。

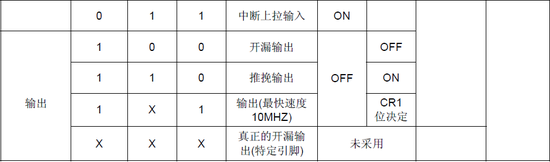

通过这个表我们可以看出配置好一个I/O口只需要DDR方向寄存器,CR1控制寄存器,和CR2控制寄存器

下面我们先来看看输入模式

将方向寄存器DDRx位清零就选择了输入模式,在该模式下读IDR寄存器的位将返回对应I/O口引脚上的电频值。

理论上可以通过软件配置得到4中不同的输入模式:悬浮不带中断输入,悬浮带中断输入,上拉不带中断输入,上拉带中断输入。但是在实际情况下不是所有的I/O口都具有外部中断和上啦,我们应该参考数据手册中关于每个引脚的实际硬件性能描述。

悬浮输入或者上拉输入

端口的输入功能是不会自动选择,用户可以通过写相应的外设寄存器的控制位来选择输入功能,通过上表可以看出我们可以通过设置DDR和CR1寄存器的相应位来配置输悬浮输入或者上拉输入。

中断功能

我们可以在I/O口引脚为输入模式时通过设置PX_CR2寄存器的相应位来配置某个I/O作为外部输入中断模式。在这种配置下,I/O引脚上的一个信号沿或者是低电频会产生一个中断请求。

在EXTI_CR[2:1]J寄存器中对于每一个中断向量都可以单独编程为上升沿或者下降沿触发。

外部中断只对I/O口设置为输入模式才有效

中断屏蔽

可以通过对PX_CR2寄存器的相应位进行编程来单独使能/关闭外部中断功能,复位后外部中断是关闭的。

模拟通道

ADC外设可以选择某些I/O口作为模拟输入通道。当使用模拟通道的时候,ADC_TDR寄存器的输入施密特触发器必须被关闭。

施密特触发器

部分I/O口包括一个内嵌的输入施密特触发器。可以通过ADC_TDR施密特触发器禁止寄存器来使能/禁止施密特触发器

输出模式

将DDRX位置1就选择了输出模式。在该模式下向ODR寄存器的位写入数据将会通过锁存器输出对应数字值到I/O口。读IDR的位将会返回相应的I/O引脚电频值。通过软件配置CR1,CR2寄存器可以得到不同的输出模式:上拉输出,开漏输出。

输出功能为单片机输出到外部或者I/O引脚提供一个方便的操作方法,输出功能使能时,输出功能模块接管了输出锁存寄存器(PX_ODR)并强制PX_ODR相应的位为1

输出功能可以是上拉或者开漏输出,取决于外设本身和控制寄存器1(PX_CR1),输出频率取决于控制寄存器2(PX_CR2)的值。

例如:

考虑达到最佳性能,SPI输出引脚必须设置为上拉,快速摆率. uart_TX可以被配置为上拉或者开漏外部带上啦来实现从机的配置。

摆率控制

摆率输出可以使用CR2的相应位通过软件控制。置位CR相应位选择为10MHZ的输出频率。该功能可以在开漏也可以用在带上啦的输出模式I/O口,输出类型为O3和O4

复位后的默认配置

复位之后,所有的引脚都是悬浮输入模式。

没有使用的引脚

没有使用的引脚必须连接到一个固定的电频。

低功耗模式

低功耗模式对GPIO口的影响

等待(Wait) 对I/O口无影响。外部中断可以腮红MCU退出等待(Wait)模式

停机(Halt) 对I/O口无影响。 外部中断可以说使MCU从停机模式(Halt)唤醒

GPIO寄存器

GPIO 寄存器表和复位值

以上寄存器值的描述是我复制stm8s手册描述。

上一篇:IAR新建一个工程

下一篇:STM8查看IO口的方法

史海拾趣

|

我司有做24G平面微带技术雷达,但目前的难点集中在DSP信号处理上,不知道论坛中是否有这方面的高手一同探讨一下;如用在交通测速测距、安防监控、液位物位测量等方面的信号处理,用什么样的DSP处理比较能突显产品的特点呢? 欢迎大家来给我意见。… 查看全部问答> |

|

我刚买了一个GPS,用的是windows embedded ce 6.0系统,却发现控制面板程序被厂商删掉了,打不开控制面板。哪位能提供一下windows\\control.exe程序?请发到 lvaj2008@gmail.com,谢谢!… 查看全部问答> |

|

哪位好心人解释下vivi 中的 nand_read_ll的NFADDR设置这段啊 void nand_read_ll(unsigned char *buf, unsigned long start_addr, int size) { int i, j; if ((start_addr & NAND_BLOCK_MASK) || (size & NAND_BLOCK_MASK)) { return ; ...… 查看全部问答> |

|

使用V5时将一个普通的IO当作全局时钟使用了,结果在MAP时,发生错误:ERROR:Place:645 - A clock IOB clock component is not placed at an optimal clock,改了系统的环境变量,加BUFG都无法解决,请问该如何解决?主程序如下: module ad_uart ...… 查看全部问答> |

|

上周就已经把CAN通讯调通了,不管是查询模式还是中断模式都跑的很好,这周给板子加了个UCOS,2.86版本的。然后把CAN通讯加上去,CAN数据死活发不出来。用lookback模式自测,发现可以收到自己发出去的数据,但是用示波器测试发送脚,就是没见到 ...… 查看全部问答> |

|

按照我的建议,将帖子归类一下: GPIO 模块 1:谁来帮解释下 GPIO 的地址掩码的意思 https://bbs.eeworld.com.cn/viewthread.php?tid=305581&extra=page%3D1%26amp%3Bfilter%3D0%26amp%3Borderby%3Ddateline%26amp%3Bascdesc%3DDESC 2:一键多 ...… 查看全部问答> |