历史上的今天

今天是:2025年03月01日(星期六)

2021年03月01日 | AMD第三代霄龙即将问市,Zen4架构、96核心

2021-03-01 来源:EEWORLD

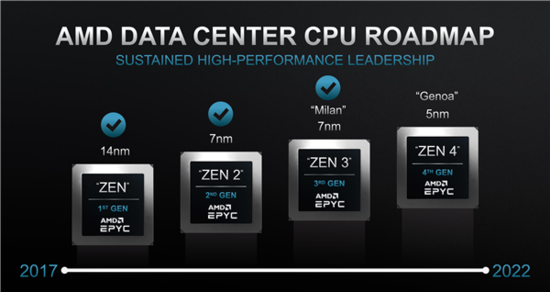

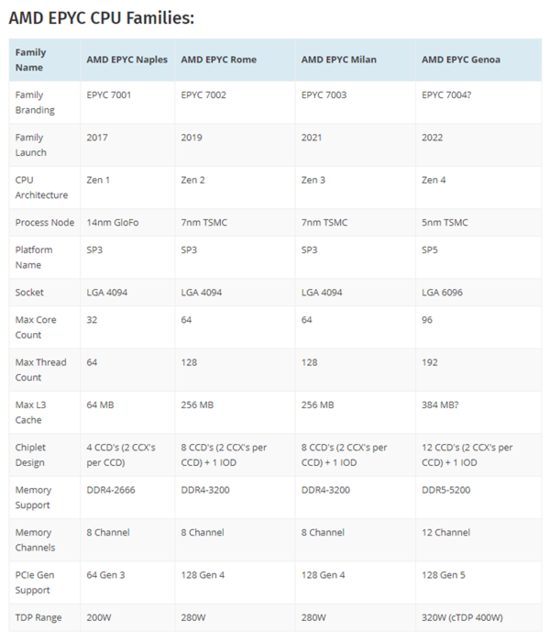

AMD将在这个月正式发布代号“Milan”(米兰)的第三代霄龙7003系列数据中心处理器,基于7nm工艺、Zen3架构,最多还是64核心128线程,支持八通道DDR4-3200内存、128条PCIe 4.0通道。

再往后,自然就将是5nm工艺、Zen4架构,代号为“Genoa”(热那亚),产品序列应该是第四代霄龙7004系列。

只是发布时间可能要耐心等等,预计最快也得2021下半年,甚至到2022年初。

现在,推特博主@ExecutableFix 首次曝光了四代的核心规格:

1、核心数量最多96个,线程数量最多196个,比现在增加整整一半。

内部仍是chiplet小芯片结构,每颗8核心,总计12颗,另外继续一颗IO芯片。

2、内存支持新一代DDR5,最高频率达5200MHz,通道数也增加一半的达到12个。

每通道2条内存,那么单路最多就是24条,使用128GB内存条的话,单路就是最多3TB内存。

3、输入输出支持新一代PCIe 5.0,单路还是最多128条通道,但是双路对外可提供160条。

这意味着,双路之间内部通信所需通道数从128条减少到96条,毕竟带宽翻番了。

4、热设计功耗最高达到320W,比现在增加40W,同时支持最高上调到400W(cTDP)。

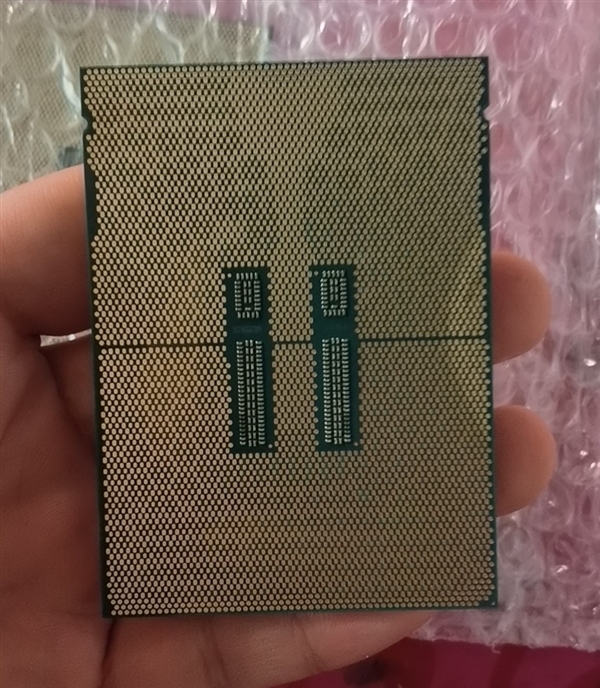

5、接口首次更换为新的SP5 LGA6096,比现在的SP3 LGA4094增加多达2002个触点。

毕竟要支持DDR5、PCIe 5.0,但有趣的是SP4的名字被跳过去了。

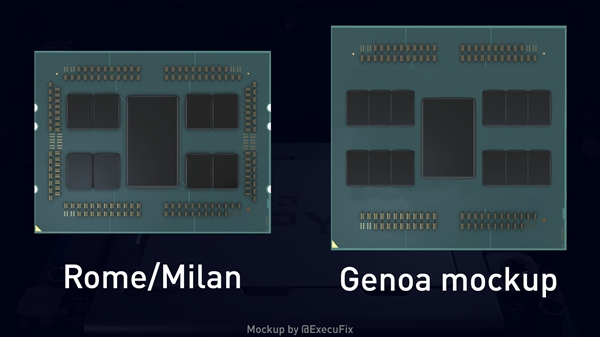

二三代霄龙、四代霄龙(模拟图)内部结构对比

竞品方面,Intel将在今年底发布代号Sapphire Rapids的第四代可扩展至强,规格同样是飞跃的,但是相比于四代霄龙各方面都逊色不少。

10nm Enhanced SuperFin制造工艺,Golden Cove CPU架构,MCM多芯封装,最多4颗小芯片、60核心120线程(至少初期隐藏4个核心),集成最多64GB HBM2e高带宽内存,支持最多8通道DDR5-4800、80条PCIe 5.0,热设计功耗最高400W,接口换成新的LGA4677-X。

下一篇:关于振荡器挑选的门道

史海拾趣

|

SDHC(SDIO接口,SD卡接口)的流接口实现一般在什么目录下? 换了一种CPU,BSP也变了. (以前是搞好EVC写的流驱动的) 对于SDHC(SDIO接口,SD卡接口). 一般来说 以下流接口 SDH_Close SDH_Deinit SDH_Init SDH_IOControl ...… 查看全部问答> |

|

小弟最近想了解下关于linux下嵌入式开发的东西,有一些简单东西不明白,希望从事这方面工作朋友或者技术达人能够给些指点。先谢谢大家。 首先是关于linux开发流程的问题。基于linux的嵌入式开发应该是一个什么样的过程呢? 之所以有这个疑问, ...… 查看全部问答> |

|

编译非BSP工程,比如MS提供的COMMON里面的串口驱动COM-MDD2.在fileview找到工程,右键勾 上 clean before build,make run_time image after build 然后build current project 如果是BSP下的驱动工程就编进NK了。可common里面的我今天照上述方式 ...… 查看全部问答> |

|

稳压器用LM7905CT,输入电容2.2uf,输出电容1uf,请问为什么滤波电容采用2.2mf,稳压器的输入电压仍然存在很大的脉冲直流电压?本人是新手,请讲的详细点,谢谢!… 查看全部问答> |

|

按照我的建议,将帖子归类一下: JTAG 模块 1:各位大虾,请教个关于jtagWait()防止JTAG失效的问题 https://bbs.eeworld.com.cn/viewthread.php?tid=305969&extra=page%3D2%26amp%3Bfilter%3D0%26amp%3Borderby%3Ddateline%26amp%3Bascdesc%3DD ...… 查看全部问答> |