历史上的今天

今天是:2025年04月25日(星期五)

2021年04月25日 | 芯片验证越来越复杂,西门子EDA是怎么做的

2021-04-25 来源:EEWORLD

“在过去的十年当中,验证成本的增长速度远高于设计。在整个前端设计当中,包括工程师、软件、硬件在内的验证资源将占到整体的70%,而设计只占30%,这说明验证在整个工作当中的占比会越来越高。”西门子EDA全球副总裁兼中国区总经理凌琳说道。

随着工艺的发展,晶体管数量达到了百亿级水平,SoC的复杂性呈现指数型增长。为了满足严苛的开发周期和开发效率,尽管相比RTL仿真开销更大,但硬件仿真的需求不断增加,并且在2018年支出增长上正式超越了RTL仿真。

正是因为硬件辅助验证的重要性,如今三家EDA巨头都有相应的硬件辅助验证系统,包括西门子 EDA的Veloce,Synopsys的Zebu以及Cadence的Palladium。

凌琳表示:“SoC的软件确认成本正在快速增长,已经超越了传统的硬件验证,这是由于SoC所处的软件环境越来越复杂,规模越来越庞大。与此同时,电源、模拟混合信号等硬件不光需要验证本身的功能,还需要在操作系统或其他软件环境中进行协同验证。”

验证的成本变得越来越高

西门子 EDA亚太区技术总监李立基也认为,如今要确保芯片开发成功,确保市场可以接受,已不再是比拼功能的高低,而是要看其软件的运行性能。“所以在芯片开发过程中,需要将软件直接跑到芯片上去收集数据。在设计的时候就需要把工作负载放到芯片上,同时进行性能和功耗的分析,并进行优化。所以在设计流程中需要验证早期介入,包括功能、性能及功耗全方位的验证和优化。”

各个环节中验证的重要程度

李立基以整个设计流程为例,介绍了仿真验证的具体环节。

首先是虚拟验证环节,也就是通过硬件模拟芯片中的各种IP,进行针对性评估与验证。虚拟验证最大的好处就是实现了软件定义SoC,因此整体设计时间大幅缩短。通过软件同硬件的结合,提早发现问题并指导设计方向,满足设计方法学中的Shift-left概念。同时,CPU并不是用RTL来实现,因此运行速度相当快,可达100 MIPS。

之后,随着硬件设计开始完善,需要Debug各种不稳定因素,就需要一些可见性的硬件加速进行辅助调试工作。

第三,芯片更加完善之后,需要评估功耗与性能,进行提取和分析,把软件工作负载导入到硬件仿真器上进行评估。

第四,随着芯片接近成熟,需要系统地进行仿真,在整个硬件系统里面进行综合,确认系统间的互动,因此可以转移到FPGA原型系统上。

硬件辅助验证系统平台介绍

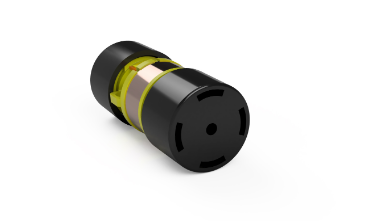

为了满足验证的四个步骤,西门子 EDA日前发布下一代全面硬件辅助验证系统平台,该系统是业内首个完整的集成式解决方案,将一流的虚拟平台、硬件仿真和 FPGA 原型验证技术融于一身。包括了用于虚拟平台/软件激活验证的 Veloce HYCON(HYbrid CONfigurable),150亿门级电路Veloce Strato+,Veloce Primo 企业级 FPGA 原型验证系统以及Veloce proFPGA 桌面 FPGA 原型验证系统。

Veloce平台四大产品家族

李立基具体介绍了该平台的四大类产品。

Veloce HYCON是业界唯一支持早期软件工作负载分析的解决方案,支持基于软件的设计方法,符合如今Shift-left的设计方法学。从而缩短整体开发时间,并使得软件和硬件的整合速度提前,以更快发现架构问题并对此进行修改。“客户可以把自己设计部分的硬件直接连到HYCON模型上,就可以执行操作系统并进行评估,因为CPU不是用RTL来开发的,所以运行速度更快,验证时间也大为缩短。”李立基说道。虚拟方案的好处是显而易见的,随着如今SoC设计越来越依赖于软件和IP,如果可以更早地在子系统环境中确认,就可以极大缩短设计、验证以及上市时间。

Veloce Strato+则是实现了2017年推出 Veloce Strato 平台时发布的蓝图。由于采用了全新专有的2.5D芯片—Crystal 3+ 的创新设计与制造,实现了更高的内部互联速度、更低的功耗以及更小的面积,使系统容量比之前的 Veloce Strato 提高了1.5倍。李立基强调,采用全定制ASIC相比FPGA虽然成本更高,但是可以实现完整的可见性,从而满足客户的验证需求。

李立基特别强调了AMD作为Strato+的合作客户,对Strato+的性能高度认同。AMD企业院士兼方法架构师Alex Star强调,“我们开发的高性能设计需要使用可扩展、可靠、创新的仿真解决方案,我们十分高兴能够与西门子合作,在 AMD 率先部署大容量 Veloce Strato+ 系统。此外,我们也非常高兴看到我们第二代和第三代 AMD EPYC处理器可以用于 Veloce Strato 和 Veloce Strato+ 平台。这两个处理器系列的高性能可以为 Veloce 生态系统及包括 AMD 在内的客户带来更高的设计生产力。”

针对FPGA原型验证系统,西门子 EDA则将其细分为企业级和桌面级两种。业级 FPGA 原型系统 Veloce Primo 可提供出色的性能,容量能够扩展至 320个FPGA,最高支持120亿个门阵列。Veloce proFPGA 桌面系列产品采用模块化的容量方案,可采用 Intel Stratix 10 GX 10M 和 Virtex UltraScale+ VU19P 的高端 FPGA,满足从 4000 万门到 8 亿门的多种容量扩展需求。

Arm 设计服务高级总监 Tran Nguyen 表示:“各行各业不断增长的计算需求意味着更短的上市时间,西门子的 Veloce Primo 企业级 FPGA 原型解决方案能够帮助 Arm 迅速解决设计问题,并实现验证目标,使我们的生态系统可以开发出基于 Arm 的高质量 SoC,从而加速创新步伐。”

如今,在FPGA原型验证领域,一些公司会选择自己开发FPGA原型验证平台,对此李立基表示,FPGA原型验证的难点不是在硬件设计方面,而是如何将一个设计切分,以布局到FPGA原型验证系统中,这个切分算法才决定了运算的性能。

平台化的魅力

凌琳指出,很多大型芯片设计公司会根据自己芯片设计需求和方向,选择不同供应商的验证系统。但针对中国市场,中小型企业会更多一些,因此无论是技术因素还是商务便利性来说,平台化解决方案更适合中国。

平台化可以最大限度地减少技术迁移的成本,比如Strato和FPGA原型验证系统具有统一性和互通性,采用了统一的操作系统、统一的解决方案、以及统一的RTL前端编译器。因此客户可以轻松实现不同阶段的RTL复用,无论是从Strato迁移至FPGA原型验证系统实现下一步验证环节,还是在FPGA原型验证过程中发现Bug,再回溯至Strato进行更高可见性的调试。这种灵活的设计能够最大限度地重用验证材料、环境和测试内容,进而为无缝方法的实施提供必要基础。

李立基另外补充道,Veloce硬件平台的APP非常多,可以将EDA传统的软件功能进行加速,也可以进行DFT加速,相当于一个平台可以实现各类工作。

同西门子的协同效应

此次发布会,是西门子EDA更名后的首次亮相,因此李立基和凌琳也解读了Mentor更名为西门子EDA背后的意义。

李立基表示,西门子所提倡的数字化双胞胎设计理念,和Mentor的仿真产品理念完全吻合。比如PAVE360从芯片到自动驾驶系统的解决方案,就是依托了Veloce Strato硬件仿真器,实现在虚拟环境中测试汽车自动驾驶的性能。

凌琳表示,公司更名不是放弃和终止,而是面向一个新的、更广阔的平台。西门子是更博大精深,更有广泛且深度的技术公司。以仿真为例,随着芯片设计越来越需要考虑要在系统中表现,需要面对更多跨领域的仿真要求。包括电子、电磁、热力学甚至机械领域。“更名为西门子EDA后,我们可以满足既有或潜在客户更广泛的研发需求,有些问题可以在芯片内解决,有些问题需要和其他系统进行协同跨领域集成与仿真,因此西门子EDA可以给客户带来系统级设计理念。”

在Mentor并入西门子的四年中,借由西门子数字化工业软件的优势和资金,收购了诸多公司,不断补充及完善系统级解决方案。

“变成西门子EDA之后,公司EDA的道路并没有终止,而是在加速延展中。”凌琳总结道。

史海拾趣

|

电子天平 ( 万分之一 ) ; 带 F ID 检测器的气相色谱仪 ( 带有分流装置 ) ; 10 μ L 微量进样器 ; 20 mL 带胶塞小玻璃瓶若干 ; 医用注射器 1 mL 、 2 mL 各两只 ; 小口径毛细柱 DB - 17HT ( Φ 0. 25 mm × 30 m × 0 .15 μ m; 最高使用温度为 360 ...… 查看全部问答> |

|

通过AD转换后得到4组word类型的AD值,分别保存在a0[8],a1[8],a2[8],a3[8]4个数组里,现在想获得a0[8],a1[8],a2[8],a3[8]的平均值,保存在一个新数组a4[8]里,应该怎么做呀?… 查看全部问答> |

|

问题描述如下: 开机黑屏看不到自检信息,AMI BOIS报警,大概响8-10下(响的有点快,数不过来),前面两下几乎是连着的,大概是1长8短。虽然看不到自检信息,但是按F2后会“滴”一下,再按回车键,硬盘灯开始闪,随后进入系统登陆界面(XP系统,要 ...… 查看全部问答> |

|

本人现在用C8051F020的SPI口线对90092进行控制,对90092进行初始化成功,但是不知道如何在屏幕上叠加字符. 比如用SPIWR()这个子程序对90092发送控制命令. 怎样才能在屏幕上有叠加字符显示?请朋友们帮帮忙,谢谢啦!急!… 查看全部问答> |

|

redhat9.0重新编译内核(2.4.20)后USB键盘无法使用的问题? 小弟现在做linux上的framebuffer驱动,在RH9上编译,内核版本也没有动,用的RH9自带的源代码。在重新编译内核时都正常,重启后, grub菜单出现2.4.20-8custom,选择后启动,到出现xwindows登录界面后,该输入用户名密码时,键盘无法使用。之前在gru ...… 查看全部问答> |

|

发现lpc1343 GPIO0_11--GPIO1_3不能做数字口 最近无意中使用LPC1343的P0.11(即AD0)做数字口输出,驱动LED,发现无法配置为数字口,不能按程序执行。于是又测试了一下其他端口,发现p1.0--p1.3也存在同样的问题,对相应的I/O配置寄存器IOCON_PIOn 进行了配置,问题依然存在,然后,… 查看全部问答> |