历史上的今天

今天是:2024年11月05日(星期二)

2021年11月05日 | 一起学mini2440裸机开发(四)--S3C2440定时器学习

2021-11-05 来源:eefocus

S3C2440定时器原理概述

s3c2440有5个16位定时器,定时器0、1、2和3有脉冲宽度调制(PWM)功能,因此这4个定时器也被称为PWM定时器。定时器4是一个内部的定时器,没有外部输出引脚。

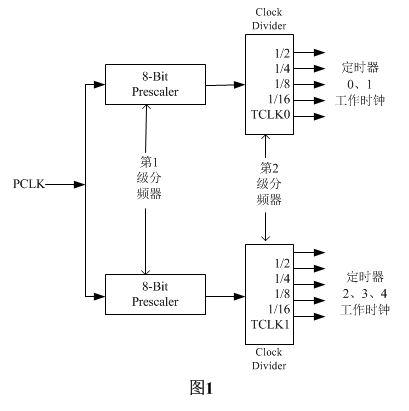

定时器的时钟源是PCLK,定时器工作所需频率并不等于PCLK,还要进一步将PCLK通过内部的分频器分频才能得到。这里也可以看出外部设备所需的工作频率不一定等于它的时钟源。其中,定时器0、1公用一个分频器,另外3个定时器公用一个分频器。分频器输入信号经过第2级分频器进一步降低时钟频率,然后输出作为定时器工作的时钟。下图为由PCLK得到定时器工作时钟的框图:

虽然S3C2440定时器有5个,但是它们的工作原理都是相同的,只需要理解一个定时器的工作原理即可。对于某一个定时器,其内部结构原理如图2所示。寄存器TCMPBn和TCNTBn用于缓存定时器n的比较值和初始值;TCON用于控制定时器的开启与关闭;可以通过读取寄存器TCNTOn得到定时器的当前计数值。注意图2所示的是PWM定时器,也就是定时器0-3,不包含定时器4,定时器4也没有外部输出引脚。

定时器工作原理概述:

● 首先,将定时器的比较值和初始值装入寄存器TCMPBn和TCNTBn中

● 然后,设置定时器控制寄存器TCON,启动定时器。此时,TCMPBn和TCNTBn中的值会加载到寄存器TCMPn和TCNTn中

● 此时,定时器会减1计数,即TCNTn进行减1计数,当TCMPn=TCNTn时,TOUTn引脚输出取反。

S3C2440定时器相关寄存器

● 定时器控制寄存器TCON

由于各个定时器的工作原理相似,下面以定时器0为例进行讲解。在定时器控制寄存器TCON中,位[3:0]用于控制定时器0,其含义如表1所示:

● 定时器比较值缓存寄存器TCMPBn、计数值缓存寄存器TCNTBn

这两个寄存器用于存储定时器的比较值初始值和计数值初始值。

● 定时器比较值寄存器TCMPn、计数值寄存器TCNTn

这两个寄存器是定时器内部寄存器,用户无需对其进行写操作。

● 定时器观察值寄存器TCNTOn

在定时器减1计数过程中,TCNTn的值可以通过TCNTOn寄存器得到。

● 定时器配置寄存器TCFG0、TCFG1

这两个寄存器很重要啊。本节开头讲过,PCLK经过两级分频器,输出频率作为定时器的工作频率,如图1所示。因此,一定要有寄存器来设置分频系数。

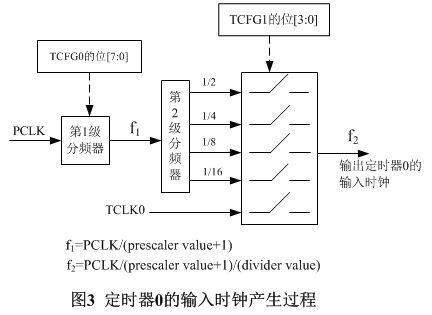

①定时器配置寄存器TCFG0用于控制第1级分频器的分频系数,分频器输出频率为:PCLK/(prescaler value+1),其中prescaler value=0~255。

②定时器配置寄存器TCFG1用于控制多路开关。divider value=2,4,8,16

定制器的输入时钟=PCLK/(prescaler value+1)/(divider value)。下图3为定时器0的输入时钟产生过程:

从图1和图3可以看出,定时器0、1公用一个第1级分频器,第1级分频器的分频系数由TCFG0的位[7:0]控制;定时器2、3、4公用另一个第1级分频器,该分频器的分频系数由TCFG0的位[15:8]控制。同时,从图3可以看到,第2级分频器的分频系数是确定的,只有5种类型:2分频、4分频、8分频、16分频和外接时钟TCLKn(n=0或1),定时器配置寄存器TCFG1用于控制多路开关,每个定时器都由其中的连续4位控制。以定时器0为例,TCFG1的位[3:0]用于控制定时器0。下图为S3C2440数据手册上关于TCFG1的说明:

下面以定时器0举例子说明定时器的配置过程。

例:设置适当的分频系数,是定时器0的输入时钟为62.5KHz。

因为PCLK为50MHz,则50MHz/62.5KHz=800,即需要对PCLK进行800分频。所以使第1级的分频系数为100,第2级的分频系数为8即可满足要求。最后,只需要将分频系数写入定时器控制寄存器中相应的位即可,代码如下:

TCFG0&=~(0xff); //设置第1级分频系数,分频系数为99

TCFG0|=99;

TCFG1&=~(0xf); //设置第2级分频系数,分频系数为8

TCFG1|=0x02; //62.5KHz=50MHz/(99+1)/8

下一节介绍两个关于定时器0的实验,在这里贴出关于定时器0的初始化代码,相信大家会理解的更好一些的。

/***************************************************************

* 函数名称:void Timer0_Init(void)

* 参数说明:无

* 全局变量:无

* 返 回 值:无

* 功 能:对于50MHz的PCLK,经过分频获得62.5KHz的定时器0

* 的输入时钟。

***************************************************************/

void Timer0_Init(void)

{

TCFG0&=~(0xff); //设置第1级分频系数,分频系数为99

TCFG0|=99;

TCFG1&=~(0xf); //设置第2级分频系数,分频系数为8

TCFG1|=0x02; //62.5KHz=50MHz/(99+1)/8

TCNTB0=62500; //1s中断一次。经过上述分频器得到定时器0的输入时钟频率为62.5kHz,即定时器

//每秒钟计数62500次。因此,初始化时,定时器0计数值初始值为62500

//在这里我们可以看出TCMPBn没有设置,因为咱们用它的默认值0,所以就不需要设置

TCON|=(1<<1); //开启手动更新位,即当定时器开启后,TCMPB0和TCNTB0中的值会加载到寄存器TCMP0和TCNT0中

TCON=0x09; //关闭手动更新位,设置自动加载位,同时开启定时器,这样,TCNT0进行减1计数,当TCNT0中的计

//数值减到0时,TCNTB0、TCMPB0中的数据分别会自动加载到TCNT0、TCMP0中并进行新一轮的减1计数

}

史海拾趣

|

某天某日某产房,你诞生了(power up , 上电运行),结果你不哭,医生把你提起来,屁股上狠狠一巴掌,你哇哇大哭(reset, 复位成功),护士给你检查,看有没有传染病(EMI测试)、然后打预防针(绝缘处理),没有问题后作记录(QC pass),你的父母来接你回去(客户验收 ...… 查看全部问答> |

|

本信息来自合作QQ群:电子工程师技术交流(12425841) 群主在坛子ID:Kata 交流并网逆变器,是不是先要用建交流小信号模型,然后用matlab仿真,然后才是主回路拓扑结构 功率器件的选择,DSP算法的实现啊? … 查看全部问答> |

|

请问这里有谁看过姜咏江写的《基于QuartusII的计算机核心设计》? 书里的rom和ram都有地址输入端,到了总线机构链接时就没了,只有bus输出端,还有标志线marL应该怎么加在rom和ram上呢? … 查看全部问答> |

|

串口调试助手软件相信大家都用得多了,下面我来介绍本人用AT89S52设计的一款硬件版的串口调试助手。^.^ 公司的许多无线通信设备需要测试串行数传功能,而传统的测试方法就是用数传线将设备的数据口与电脑串口连接,使且串口调试 ...… 查看全部问答> |

|

Advances.in.Mobile.Radio.Access.Networks. Advances.in.Mobile.Radio.Access.Networks.Artech.House.Publishers.Jun.2005.eBook-LinG… 查看全部问答> |