历史上的今天

今天是:2024年11月18日(星期一)

2021年11月18日 | 芯耀辉,高速数字电路不可或缺好伙伴

2021-11-18 来源:爱集微

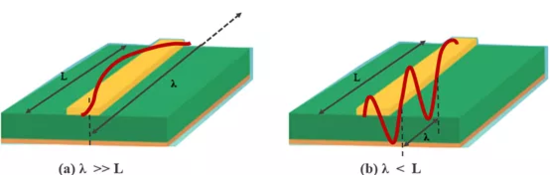

随着芯片产业的蓬勃发展,对数据传输速率的需求也与日俱增。早期的产品应用(例如:I2C、SPI等),信号速率大约为Kbps-Mbps量级,信号波长远大于传播结构的几何尺寸,基尔霍夫电压电流定律即可处理大部分电子电路现象;如今的产品,其信号速率动辄高达数Gbps(例如:DDR5 4.8Gbps以上、PCIE Gen4为16Gbps、USB3.1 Gen2为10Gbps),信号波长已小于结构几何尺寸,信号传送以电磁波方式行进,就必须考虑波的反射、传播以及干扰,对应到信号的指标即为S参数S11(反射)、S21(传递损失)、S31 & S41(近端或远程串扰),信号传送时所产生的高频现象,已成为信号完整性设计中不可忽略的因素。(图1)

(a)信号变化远大于信道的几何尺寸 (b)信号变化小于信道的几何尺寸

图1:不同传输速度下电磁波的效应

什么是信号与电源完整性(Signal & Power Integrity,简称SIPI)

Signal Integrity(SI)又称信号完整性,是一种对于信号传送质量的分析领域,即在互连通路中保持信号的完整传递,使芯片工作不受影响。举例来说,芯片就像一部跑车,互连通道(channel)就像高速公路或赛道,如果有障碍物或车子高速行驶而尘土飞扬(反射&串扰),再好的跑车都很难安全抵达目的地。

Power Integrity(PI)又称电源完整性,是分析系统在输出(through-put)状态时,如何让负载电流的变化引起的电压扰动保持最小。电源完整性的好坏直接决定了数据传送时序的一致性,其中任何设计缺失,都有可能导致系统出现功能错误。例如生活中,吹风机的开关造成电力网络瞬间压降,电视画面即刻出现雪花噪声。良好的电源完整性设计,不论负载状况如何,总是能够提供稳定的电压,使芯片工作在稳定偏压区间而有最佳表现。

常见的SIPI分析指标

无论是信号还是电源的完整性,皆可从频域&时域着手分析。

信号完整性(Signal Integrity)

频域部分,主要是观察互连信道S参数的频率响应,例如:

(1)S21(信号传递) & S11(信号反射)

(2)S31 & S41(近端或远程串扰,意即Near-End & Far-End Crosstalk)

频域的检测,可快速确认通道好坏,判断是否符合协议规范,做出初步的筛选。

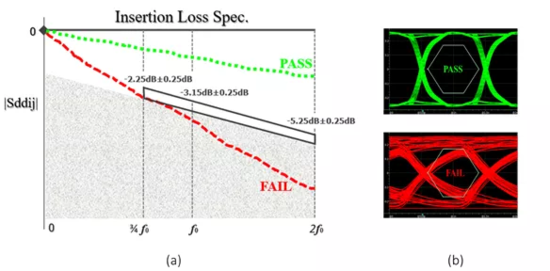

以图2(a)为例:

协议有针对互连定出S参数规范,可通过模型提取,知道信道的好坏。

图2:(a)典型|S21|规格(b)两种情况(Pass vs Fail)

对应的眼图

时域部分,主要是看瞬时分析,例如:

(1)眼图(Eye Diagram),如图2(b)

(2)过冲/下冲(Overshoot/Undershoot)、延迟时间(Delay time/Skew)、时域反射法(Time Domain Reflection,简称TDR)等

电源完整性(Power Integrity)

频域部分

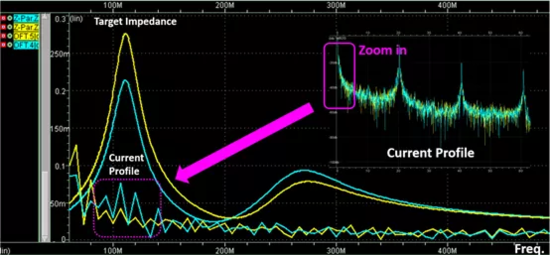

从VRM(VoltageRegulator Module)到芯片端的供电路径形成系统的电源网络(PDN:Power Distributed Network)。透过观察电源输入阻抗(Z参数)的频域响应,其大小值是否在既定限制之内,这个限制称为目标阻抗(Target impedance)。

目标阻抗的确定可以根据IC可容忍的电压变化(∆V)和负载电流的频域响应来决定。频域检测的最大好处是快速确认PDN设计是否符合基本要求,并通过不同位置摆放不同电容的迭代,以达到优化PDN的目的。

时域部分

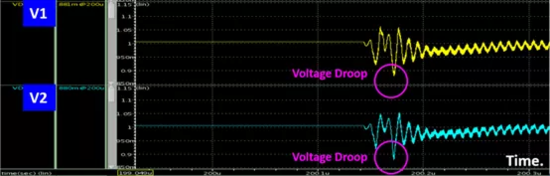

利用抽载电流与目标阻抗的关系,可以得到瞬间动态压降值(Voltage Droop),如下图3所示:

(a)

(b)

图3:(a)目标阻抗与抽载电流频谱的相对关系(b)时域仿真结果

芯耀辉SIPI系统设计与仿真团队的独特性

作为一家专注于半导体IP研发设计并且兼具客户服务的高科技公司,如何能成功的帮助客户将IP实际运用在产品上,售前与售后服务就变得格外重要。芯耀辉打破传统SIPI仿真团队的作战模式,跨领域的网罗各方面顶尖人才,无论是在封装设计、SIPI仿真,还是硬件设计上,都有丰富的实战经验。聚集这三个领域的人才,可完成上下垂直整合且具SIPI观念的规划设计,进而达到效能优化。芯耀辉SIPI团队的独特优势在于:

独特优势一:专注于专业知识,并将其融入实战中,具有独特的仿真方法

SIPI的核心是电磁行为与电路的交互作用。除了工程电磁领域相关的背景,还必须对电子电路、信号处理、数值分析有一定的了解,才能做到融会贯通,并通过此电磁领域的分析,集中火力找到问题核心。

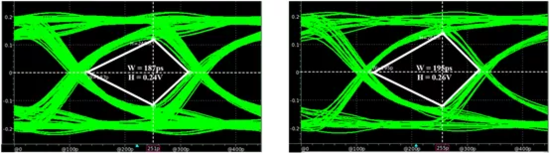

举例来说,芯耀辉团队开发了一套特殊码流分析,运用在高速接口仿真中,可以快速定位缺陷,该分析方式即利用通道中电磁干扰造成速度差异,创造出Worst SI Pattern(图4a)(包含Crosstalk,ISI,Mode conversion,etc)。如下图4为DPHY TX仿真,通过码型的不同,相同的通道下可产生出具有差异化的眼图结果,如果使用传统的PRBS7(图4b)做仿真,有一些SI缺点是无法被识别的,如果仿真无法涵盖最差的情况,就无法精确的考虑整个系统的timing budget。

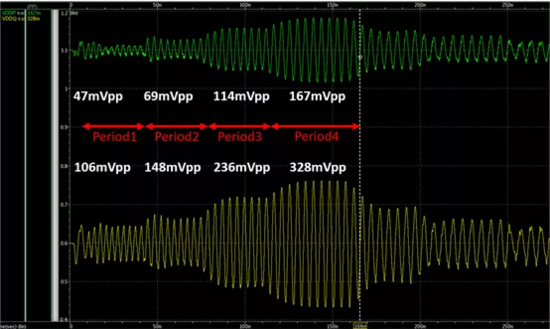

图4:(a)芯耀辉Worst SI Pattern(b)一般PRBS7码型眼图比较

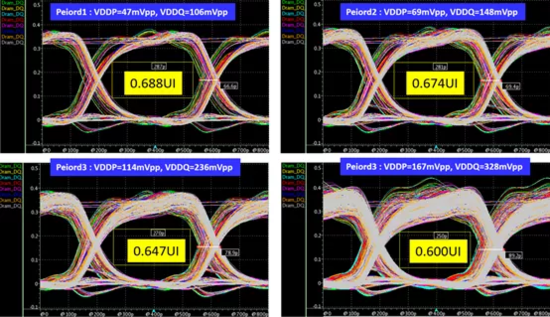

此外,结合之前长期积累的丰富经验,通过上述目标阻抗与抽载电流频谱的关系,开发出一种极差PI情况的码型。时域仿真时,产生渐进式的电源噪声,可用来判别芯片电容值(On-Die Decap values)是否足够,判别的依据即眼图是否能在如此大的电源噪声下仍清晰。如下图5所示,为不同电源噪声下,眼图的变化结果。

(a)

(b)

图5:(a)电源噪声(b)电源噪声与眼图结果比较

独特优势二:上下垂直整合的设计,在项目初期即抢得先机,奠定成功基石

一般大家对SI & PI的定位,常常是硬件工程师在投板之前,顺便做个仿真来确保Layout的质量,质量不佳时,才开始对信号电源走线做局部优化修改。但这样的方式很可能会遇到由于Bumps & Balls位置不佳,而限制了走线优化的情形,尤其是PKG Bumps与芯片端直接相连,如果因为分析结果不佳,需要动到芯片设计时,恐怕为时已晚,严重的甚至会影响项目的进程。当然,SIPI仿真也失去了预防胜于治疗的实际意义。

芯耀辉SIPI团队在芯片早期Floorplan规划时就参与讨论设计,通过团队成员与客户做深入沟通了解产品的需求,快速准确地找到具有价值的系统解决方案,可提供稳固的SIPI硬件设计,并逆向的驱动Floorplan的摆放,通过此方式可以保证所设计的产品在芯片及系统层级的SI、PI设计均为优异状态。

实例一:BALLMAP & 板端设计兼容不同类型DRAM颗粒

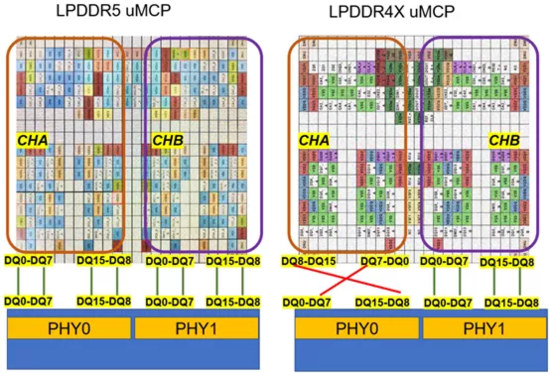

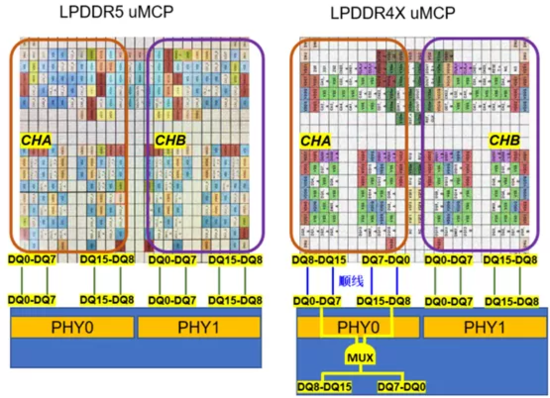

一个项目往往必须兼容不同DRAM颗粒。芯耀辉SIPI团队在LPDDR兼容议题下了苦功,针对LPDDR4X/4 & LPDDR3 & LP DDR3 Discrete兼容以及LPDDR5 & LPDDR4X & LP4 Discrete兼容,目前已有完整的封装&硬件设计解决方案。举例来说,如果比较JEDEC协议上LP5 uMCP & LP4X uMCP的Ballmap定义,会发现LP5在CHA & CHB是呈现镜像的,此时如果照着设计且又必须兼容LP4X,势必LP5或LP4X在PCB上会有交错走线的情形,严重影响DDR信号质量。在项目前期,有经验的SIPI团队即会发现问题并反馈给DDR integrator,促使在DDR PHY或DFI中实现MUX功能,进而完成Byte Swap来解决因走线交错而产生的SI风险。

(a)

(b)

(a)走线交错的情况 (b)走线顺线的情况

图6:芯耀辉提出的LP5 & LP4X兼容的设计方案

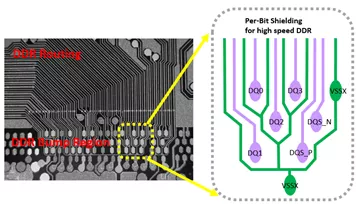

实例二:Bump Pattern设计决定了封装上信号走线的方式

图7为Flip-Chip封装DDR走线分布。高速DDR信号之间为了有较好的抗干扰能力,通常会在信号间加入Guard traces防护;由于DDR I/O数量多,为了维持竞争力,常常会将Bumps排到第二、三列,进而将PHY所占面积最小化,此时二三列信号会从第一列Bumps间过线,Bump pitch的大小即成为Bumps之间可以过几根线的重要关键,以下图(图7)而言,必须让Bumps之间能过三根线,才能达成DDR DQ Per-Bit Shielding。

因此,SIPI工程师必须在初期就很清楚该信号布局方式,并尽早与IP Designer一同规划bump pattern设计,这样封装DDR走线才会是更好的情形。

图7:DDR PKG Routing & Bump pattern Design

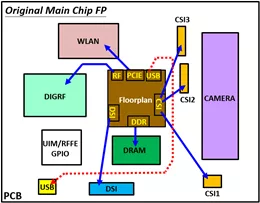

实例三:Floorplan中IP的位置也需由板端组件的摆放来共同决定

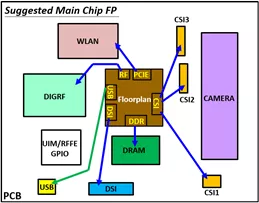

以图8手机板为例,受限于产品结构设计,USB连接器位于整个PCB板的左下方,然而USB3.1在Floorplan上却是在北边偏东,间接造成高速信号USB的走线必须绕大半圈才能从主芯片接到左下连接器,不仅走线困难度增加,信号的质量也因为走线变长而存在信号完整性的风险,此时无论怎么去优化走线,也是杯水车薪,于事无补。

如果在项目早期,有个熟悉系统设计且具备SIPI观念的工程师,在Floorplan摆放时即参与讨论,定能从系统的角度去修正此问题。举例来说,不将USB摆在北边,而是放在西边,如此一来USB3.1长走线的风险也可迎刃而解。

图8:手机板组件摆放与Floorplan对应关系

独特优势三:与CTS测试流程做结合的SIPI仿真

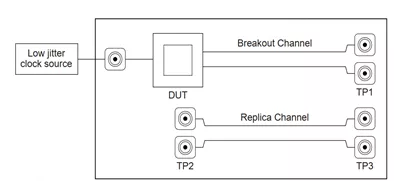

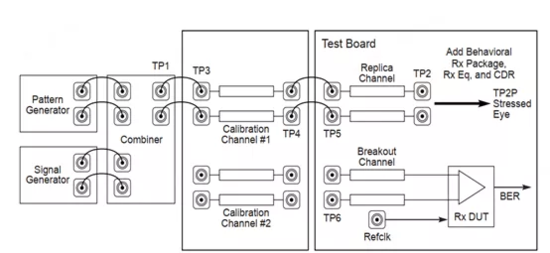

一味的闭门造车,只做仿真而不与实际量测结果做比对,将失去仿真预防胜于治疗的意义。芯耀辉团队深知比对(Correlation)的重要性,因此通过软硬件部门的紧密合作,积极地导入相关高速接口协会所定义的一系列测试流程,例如下图9为常见的高速接口TX & RX测试架构示意图(PCIE5)。透过信号测试流程,可以针对仿真流程与模型的准确度做修正,之后对仿真结果也更有信心。

(a)

(b)

(a)TX Test Board for Non-Embedded Refclk

(b)RX Test Board Topology for 16.0 and 32.0 GT/s

图9:高速接口测试架构示意图

(来源: PCI Express Base Sepcification Revision 3.0)

独特优势四:提供完整IBIS-AMI模型

随着高速信号芯片的复杂度提高,功能也越来越丰富。在高损耗的长通路连接下,CTLE、FFE、DFE等都成为高速通路常见的均衡方式,传统IBIS模型只具有芯片的IO行为,对于这类型的信号仿真有很大的局限性,而IBIS-AMI应用即因此而生。芯耀辉一直以先进高阶IP产品为主,具有完整IBIS-AMI建模流程:IBIS-IO的抽取、均衡器参数提取、AMI执行程序到EDA tool的相互作用、验证不同损耗下的准确性。提供IBIS-AMI能够让客户快速得到准确的链路SI/PI仿真,缩短产品开发时间。

史海拾趣

|

关于这个移植到问题好像pm了版主好多次,于是我决定还是发帖一记吧,谢谢之前daichen版主的帮助的。但还有问题。 移植完毕后,在测试OSStartHighRdy函数是否成功时,出现很多警告信息: 1)单步调试进入OS_CORE.C中的指令ptcb = OSTCBFreeList;&n ...… 查看全部问答> |

|

很多朋友都在学习单片机或是想学单片机,但在看了一些资料后,要么感到不知道学的什么,要么找不到下一步的学习方法,这都很正常,因为单片机的学习是一项综全性知识的结果。那么怎样学习单片机,怎么样学好单片机是我们关心的,通过我本人的学习过 ...… 查看全部问答> |

|

我写的一个驱动程序,是一个流驱动,其他没什么问题,就驱动入口函数上提示被重复加载,奇怪了,麻烦大家帮忙解决一下。感激! error C2731: \'DllMain\' : function cannot be overloaded DllMain就是驱动的入口函数。… 查看全部问答> |

|

楼主说2812允许中断嵌套,是不是可以这样理解: 比如说,程序正在执行EVA的周期中断ISR,而CPU定时器的周期中断时间到了,就会先去跳转 执行CPU的ISR,执行完再回来执行EVA的ISR。 问题: 而我在上述两个中断都打开的情况下,单步调试,在EVA中 ...… 查看全部问答> |

|

设计一个秒表,分辨率为0.01s,分三个位,分钟位,秒位,毫秒位,前两个是六十进制,后一个是一百进制,写四个文件,一个分频文件,一个10进制计数器,一个六进制计数器,一个数码管的显示文件,实验要用到两个频率,一个时钟频率,产生0.01s的时钟 ...… 查看全部问答> |