历史上的今天

今天是:2024年11月24日(星期日)

2021年11月24日 | 晶圆代工强强对战!台积电、三星先进制程大比拼

2021-11-24 来源:爱集微

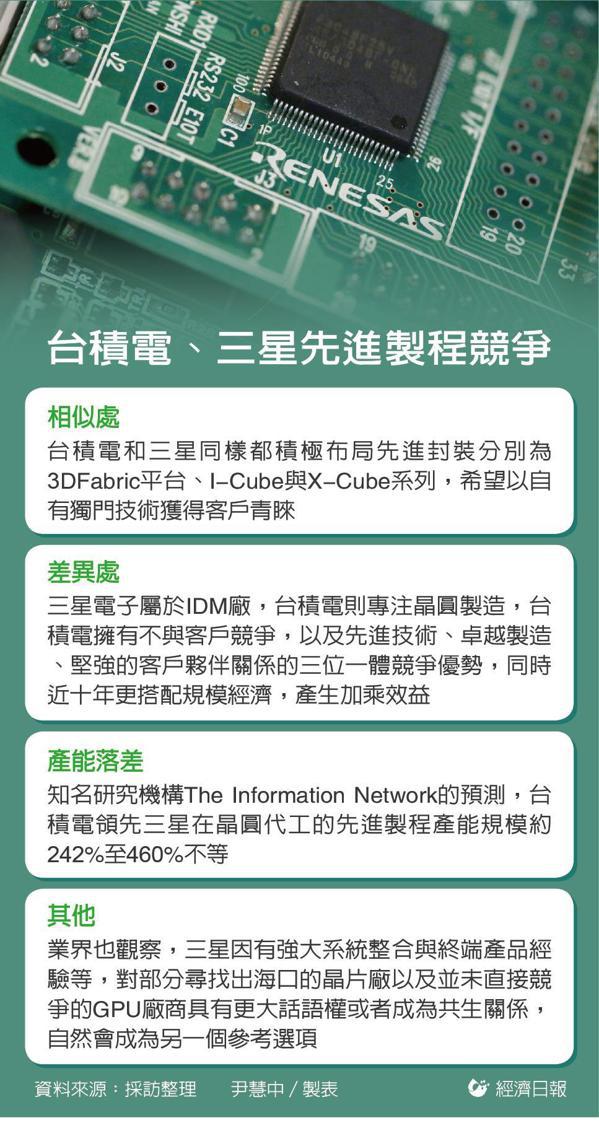

台积电和三星在先进制程竞争激烈,互抢对方客户之事屡见不鲜。根据研究机构调查数据,今年乃至明年间,台积电与三星在晶圆代工产能投资将居全球前二大,形成两强对决局面,在商业模式、产能规模、技术上的三大差异,让二者之间竞争消长一直都是业界话题。

二家厂商英雄所见相同之处,都是在先进制程技术以外,积极布局下游先进封装领域。包括3DFabric平台、I-Cube与X-Cube系列,希望结合先进制程,加上独门的先进封装技术,以完整的解决方案,争取客户青睐。

不过,两家厂商有三大差异,最大差异当属商业模式,三星和英特尔同样有整合元件(IDM)业务领域,但台积电一开始就鼓励IC设计厂商“fabless”,以自身专注晶圆制造为客户服务。台积电不与客户竞争,加上先进技术、强大制造、坚强的客户伙伴关系等三位一体竞争优势,近十年培养出规模经济,彼此间有加乘效益。

不过,业界观察,三星因有强大系统整合与终端产品经验等,对部分寻找出海口的芯片厂来说具有更大话语权,比如和芯片客户谈代工也谈订单,在三星晶圆代工厂投片,将有可望在三星旗下品牌导入采用。

三星是全球前二大智能手机品牌,年出货量约2.4亿支,调整自制与采购芯片自然产生彼此平衡力道。例如三星往IDM模式发展,对其他直接竞争的手机品牌的投片生产当然较难争取,但若非直接竞争者的芯片或GPU厂商,相对无利害关系,找三星代工就是一个参考选项。

第二大差异是量产规模决定了代工地位,因三星晶圆代工的先进制程产能仅约台积电四分之一,其中产能有五成以上自用,仅约四成释出接单,总产能仍少于台积电,不少投片生产的客户多将三星代工当成第二供应商的考量。

双方PK最厉害的应该是先进制程的量产规模,代表了最直接的竞争力。虽然三星常把超越台积电挂在嘴边,但知名研究机构The Information Network预测,台积电和三星在7纳米乃至更先进的制程上,实际量产产能规模差距近三年仍相当明显。

以7纳米来看,2019年时台积电7纳米产能约每月10.5万片,对应三星制程的相关产能则仅约2万片,2020年二者之间产能差距推估约14万片与2.5万片,台积高出三星4.6倍。

同样的情况也在5纳米制程上发生,机构数据显示,推估台积电5纳米月产能将在今年内达到月产12万片,三星也积极在韩国本地扩充,估计月产能有机会达到3.5万片,台积电仍超过2.42倍。

第三大差异,市场估计将落在3纳米制程技术上。三星在3纳米先进制程的实际量产目标已调整为2022年上半年先量产第一代3纳米,采用环绕闸极技术(Gate-All-Around;GAA)精进制程,提高量产良率。台积电目标在2022年下半年量产3纳米,仍采用鳍式场效电晶体(FinFET)技术。

三星同时开发3纳米乃至2纳米所需的第二代技术多桥通道场效应电晶体(Multi-Bridge-Channel FET;MBCFET),希望在第一代3纳米量产后一年导入生产。三星指出,新技术能使芯片效能较7纳米制程提高35%、面积减少45%,功耗降低五成。但并未明讲实际量产情况,尚须持续追踪。

台积电仍计划使用FinFET架构提供客户3纳米制程产能,并在法说会上强调,将提供客户最成熟的技术、最好的效能及最佳的成本,对照5纳米及7纳米的开发与导入时间,台积电选择多种的成本组合让客户选择,让高效能运算及智能手机应用上都有较多客户使用3纳米。

史海拾趣

|

本帖最后由 paulhyde 于 2014-9-15 09:11 编辑 关键字: 晶振 振荡器 石英晶体 石英晶体振荡器是高精度和高稳定度的振荡器,被广泛应用于彩电、计算机、遥控器等各类振荡电路中,以及通信系统中用于频率发生器、为数据处理设备产生时钟信号和为特 ...… 查看全部问答> |

|

用两个传统的573 控制 数码管显示,奇怪的是单个显示时,一切正常。待到多位扫描显示时,就出现了奇怪的顺序和段码,小弟不才, 望大虾们,不吝赐教! #include <reg52.h> sbit dula=P2^0;sbit wela=P2^1; void delay(int i){ int j=1 ...… 查看全部问答> |

|

我在公司里做毕业设计,采用lpc931单片机,想把一个十六位的数字量用单片机的Pwm功能给转换成模拟量,pwm输出采用rc滤波,但具体的c程序该怎么写呢?请指教!!… 查看全部问答> |

|

Andrew Armutat 产品市场部 吉时利仪器公司 减少机架所占空间。新的吉时利SMU采用了2U[1]高的半机架设计,大大提高了机架密度。在实际情况下,基于该设计的自动化系统容量很容易集成几个到16个通道,甚至于128通道[2]也是有可能的 ...… 查看全部问答> |

|

main(void) { /*PC4 PC13 PB10 PA0 */ USART_InitTypeDef USART_InitStructure; USART_InitStructure.USART_BaudRate = 9600; USART_InitStructure.USART_WordLength = USART_WordLengt ...… 查看全部问答> |

|

使用usb(ch376或者ch375)完成PC和FPGA的通信 只是读写。 写,pc上的信息通过USB写如FPGA在数码管上显示。 读,读FPGA,ram里的信息,传给PC。 现在编verilog代码出现问题了。 谁要是有这个代码更好。 如果没有我想问一下,CH376并行通信的芯片中断管脚是怎么 ...… 查看全部问答> |