历史上的今天

今天是:2026年03月14日(星期六)

2023年03月14日 | 单片机数/模转换器的概念(A/D)

2023-03-14 来源:elecfans

前言

模数转换可以说是单片机最重要的功能了,应用场合也非常多。这篇文章主要是对其基本概念做个解释。

文中涉及的模数电概念我都链接了百科知识,不明白的可以直接跳转观看。

正文

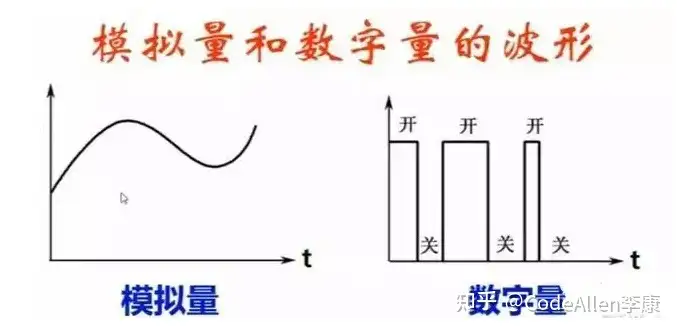

首先这里的模数指的是模拟信号和数字信号,也就是analog和digital,模/数转换就是将连续变化的模拟信号转换为离散的数字信号。(反之亦然)

这里主要是说下模数转换,因为对于控制算法开发,比如智能车或者无人机,经常需要对外部电压进行测量。但是电压是不断变化的,并不是固定的数值。开发者如果想知道具体的电压大小,就需要通过代码进行运算,而运算的参数都得是数字量。这就涉及到怎么把电压转为数值。

这就用到了模数转换器,而模数转换简单的原理就是对电压高低进行量化,这里有个模拟量和数字量的概念。

原始的模拟量是连续的,每个点都有数据,经过AD转换之后变成了离散的数字量,相对于对原始的模拟信号进行了等间隔的抽样。

但是这个等间隔,因为是单片机运行也是有时钟周期的,所以再快也是有时间的。所以也就没办法做到真正的量化,因此,一般就认为只要采样的密度足够高,能表征原有信号的一些特点就好。

这里就引出了采样密度多大合适的问题?

理论上当然是越快越好,因为越快采样点就越密集,也就越接近原始的模拟信号。但是实际过快的采样频率会消耗处理时间,增加数据处理的工作量。因此,有一个最低采样密度的标准,也就是香农采样定理,也称奈奎斯特采样定理。

香农采样定理提出,为了不失真的恢复模拟信号,采样频率应该不小于模拟信号频谱中最高频率的两倍,就是最低采样密度标准。比如220V交流电最快频率为50Hz,那么理论上最低采样频率就是100Hz。但是实际使用过程中,采样频率至少应该是最低采样频率的5到10倍才行。

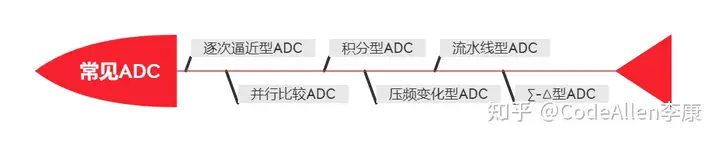

说回ADC模块,目前常见的ADC有以下几种:

具体解释可以参见文章:AD转换器的种类

目前在单片机应用比较多的,例如stm32主要是逐次逼近型ADC。

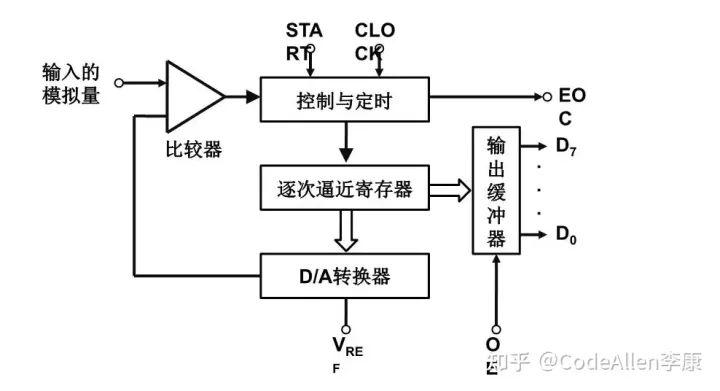

逐次逼近的过程其实就和天平秤东西的过程很像。先放最重的砝码,如果还轻,则砝码保留,否则移去。在加第二重砝码,以此类推,直到加到最轻的砝码。所有留下的砝码相加就是该物体的重量。

对应ADC的话,就是将输入的模拟信号与不同的参考电压做多次比较,使转换所得的数字量在数值上逐次逼近输入模拟量的对应值。

逐次比较型AD由一个比较器和DA转换器通过逐次比较逻辑构成,从MSB开始,顺序地对每一位将输入电压与内置DA转换器输出进行比较,经n次比较而输出数字值。其电路规模属于中等。其优点是速度较高、功耗低,在低分辩率(<12位)时价格便宜,但高精度(>12位)时价格很高。

下一篇:单片机定时器和计数器的概念

史海拾趣

|

急需!!! 电子技术研发设计开发方案!!! 公司拓展,急需方案,请拥有方案或部分技术的公司和个人迅速与我联系, 邮箱 rdeasy@yahoo.cn 请注明公司全名或个人的姓,详细准确的联系方式和方案,否则不予考。 你有别的电子技术设计 ...… 查看全部问答> |

|

我现在在学习omap5910 在ARM与DSP数据传送时遇到一个问题 就是ARM是默认的小端存储 DSP是默认的大端存储 但在网上搜索了一下 好像ARM端的大小端可以自己设置 请问哪位大虾能赐教一下 自己如何设置… 查看全部问答> |

|

430串口中,有个R/D控制线,在接收上位机的数据,但本身的数据有无发送完毕不知道啊,什么时候才可置低R/d位来接收数据啊?好像430没有发送完中断标志… 查看全部问答> |

|

MSP430的端口有P1、P2、P3、P4、P5、P6、S和COM(型号不同,包含的端口也不仅相同,如MSP430X11X系列只有P1,P2端口,而MSP430X4XX系列则包含全部上述端口),它们都可以直接用于输入/输出。MSP430系统中没有专门的输入/输出指令,输入/输出操 ...… 查看全部问答> |

|

各位前辈,我是FPGA的新手,但是我一直在思索FPGA与农业的结合点,尤其是与山区农业的结合点,因为我就是山区的,甚至在我们那边的农村生活是多么的不方便,而现代机械在山区的使用由于地势的原因,受到了很大的限制,因此我想能否用FPGA对山区的农 ...… 查看全部问答> |

|

TI【免费样片!高棚灯 LED 照明/化学/气体传感器/LED 阵列驱动,,立即获取!!!】 【免费样片! 数量有限, 立即获取!!!】TI整合国半(NS)后推出系列系统解决方案 从通讯、计算机、消费类电子到汽车、工业,从能源、医疗到安防、航空航天,收购国半之后的TI整合双方优势,不断提升产品结合后的总体效用,已陆续推出一系列创新、完 ...… 查看全部问答> |

|

1. 移位运算符移位运算符是双目运算符,将运算符左边的操作数左移或右移运算符右边的操作数指定的位数,用0来补充空闲位。如果右边操作数的值为X或Z,则移位结果为未知数X。Verilog HDL中有两种移位运算符:(右逻辑移)。 例程1 &nb ...… 查看全部问答> |