应对3D NAND新挑战,泛林Striker ICEFill电介质填充技术

2021-02-22 来源:EEWORLD

对3D NAND、DRAM和逻辑芯片制造商来说,高深宽比复杂架构下的填隙一直是一大难题。对此,泛林集团副总裁兼电介质原子层沉积(ALD)产品总经理Aaron Fellis介绍了Striker®FE增强型ALD平台将如何以其高性能推进技术路线图的发展。

沉积技术是推进存储器件进步的关键要素。但随着3D NAND堆栈的出现,现有填充方法的局限性已开始凸显。

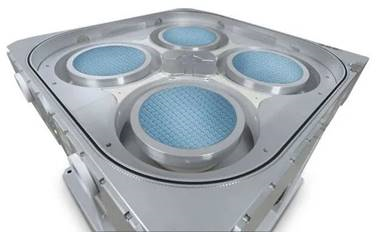

泛林集团去年推出的Striker®FE增强版原子层沉积(ALD)平台可解决3D NAND和DRAM领域的半导体制造难题。该平台采用了被称为“ICEFill”的先进电介质填充技术,可用于先进节点下的3D NAND和DRAM架构以及逻辑器件。泛林集团副总裁兼电介质ALD产品总经理Aaron Fellis指出,填充相关技术的需求一直存在,但原有的那些方法已不能满足新的需求,尤其是3D NAND堆栈越来越高。他表示:“除了堆叠层数非常高以外,为了能整合不同步骤,还要通过刻蚀来满足不同的特征需求。最终我们需要用介电材料重新进行填充,这种材料中最常见的则是氧化硅。”

Fellis指出,化学气相沉积、扩散/熔炉和旋涂工艺等半导体制造行业一直以来使用的传统填充方法总要在质量、收缩率和填充率之间权衡取舍,因此已无法满足3D NAND的生产需求,“这些技术往往会收缩并导致构建和设计的实际结构变形”。

由于稳定、能耐受各种温度且具备良好的电性能,氧化硅仍然是填隙的首选材料,但其沉积技术已经有了变化。以泛林集团的Striker ICEFill为例,该方案采用泛林独有的表面改性技术,可以实现高选择性自下而上的无缝填充,并同时能保持原子层沉积(ALD)固有的成膜质量。

Fellis表示:“标准ALD技术能大幅提升沉积后的成膜质量,这样就解决了收缩的问题。”

采用ICEFill先进电介质填隙技术的Striker®FE增强版原子层沉积平台可用于3D NAND和DRAM架构的填充。

在Fellis看来,即使能通过高密度材料实现良好的内部机械完整性,标准ALD仍可能导致某些器件中出现间隙,而且其延展性可能出现问题。而采用自下而上填充的ICEFill则能实现非常高质量的内部成膜且不会收缩。“它的可延展性非常高。”他表示,这意味着可用其满足任何步骤的填充需求,包括用于提升机械强度和电性能等,“在所制造的器件内部某一特定间隙中,填充材料都具有统一的特性。”

用于存储器件的沉积技术有自己的路线图,而推动其发展的各种存储技术进步也同时决定了现有技术的“保质期”,Fellis表示,“技术将向更高和更小发展”。预料到3D NAND堆栈增高带来的挑战,泛林集团早已开始着手改进其Striker产品。他说:“随着客户按自己的路线图发展,我们看到他们需要提高成膜性能的需求。堆叠依然是创新的推动力。”

美国半导体产业调查公司VLSI Research总裁Risto Puhakka表示,作为ALD技术的主导者,泛林集团的技术需求反映了存储行业的普遍需求,即通过提升存储密度来满足人工智能等应用的高存储需求,但同时还要避免成本提升。而3D NAND等存储器件随着堆栈高度不断提升,对填充技术也提出了更高的要求。Puhakka说:“堆栈相关的制造难题越来越多,芯片制造商也会担心花费过高的问题。”在这种情况下,继续使用非常熟悉的材料(例如氧化硅)有助于更好地预测成本。

- 线边缘粗糙度(LER)如何影响先进节点上半导体的性能

- 氦气紧缺,泛林是如何应对的?

- 泛林硅部件推动产业发展

- 泛林全新刻蚀技术,推进3D NAND和DRAM技术演进

- 解决晶圆制造难题,从概念到批量生产,泛林升级MEMS制造

- 泛林全新ICEFill™技术让3D闪存密度进一步提高

- 泛林Dr.Rick Gottscho:下一代芯片在堆叠、微缩方面的挑战

- 泛林集团先进的Striker® FE平台,为下一代器件创新赋能

- 一项革新性等离子刻蚀技术诞生—泛林集团全新Sense.i平台

- SK 海力士宣布量产全球最高的 321 层 1Tb TLC 4D NAND 闪存,计划 2025 上半年对外出货