硬件仿真工具首次超越软件Simulation的原因是什么

2020-09-10 来源:EEWORLD

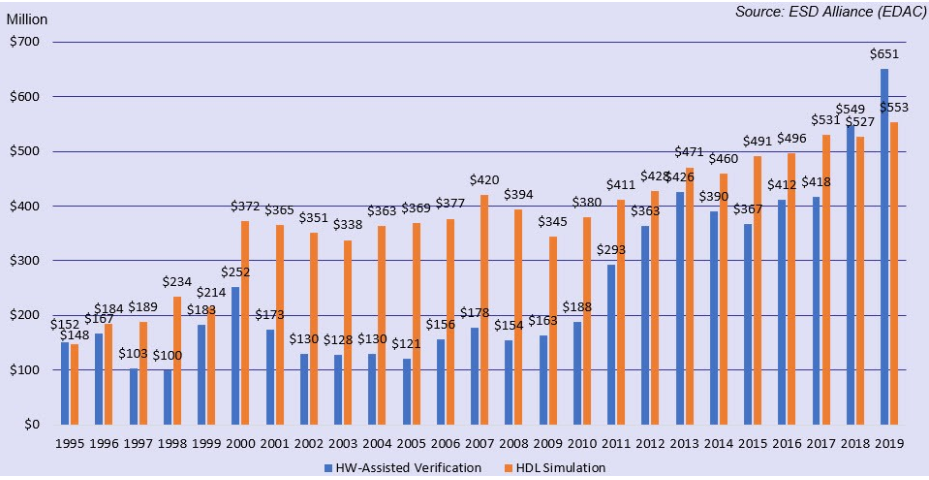

在过去的两年里,EDA领域发生着一件需要引起重视但似乎没人关注的动向:硬件验证工具(基本上是硬件仿真和基于FPGA的原型验证)的收入超过了HDL或RTL Simulation的收入。

ESD联盟每季度发布的统计报告显示,从1995年到2018年,HDL Simulation的收入一直超过硬件仿真工具1亿美元左右。

然而这一情况在2018年开始逆转,并于2019年,硬件仿真工具销售额超过了Simulation。

为什么会发生这种情况?是否有合理的理由去预测未来?

从历史谈起

在2000年初,最先进的工艺技术节点差不多是180nm,差不多是千万量级的晶体管数量,设计结构由单核处理器、内存块和硬连线逻辑(以一些商业IP和自定义块的形式)组成。

一般都是在RTL设计上运行HDL Simulation,以及通过硬件验证语言(HVL)测试台进行测试,就可以很好地满足硬件设计验证。当时硬件仿真工具还处于初级阶段,仅在电路内仿真(ICE)模式下部署,并处理真实世界的输入,以执行CPU和GPU的系统级验证。

当时,嵌入式软件并不流行,在开发时,它的验证要么在RTL达到稳定后基于FPGA的原型上完成,要么在预生产的芯片Demo上完成。

在随后的二十年中,工艺技术节点不断缩小,硬件设计的复杂性继续增加。这种方法学形成了一个多层次的结构,包括各种处理核心、大量内存以及许多IP和自定义块。今天,最大的设计接近100亿个晶体管,增加了三个数量级。

在硬件扩展的同时,软件也实现了更多的功能。与硬件一样,软件采用多层分层堆栈的形式。

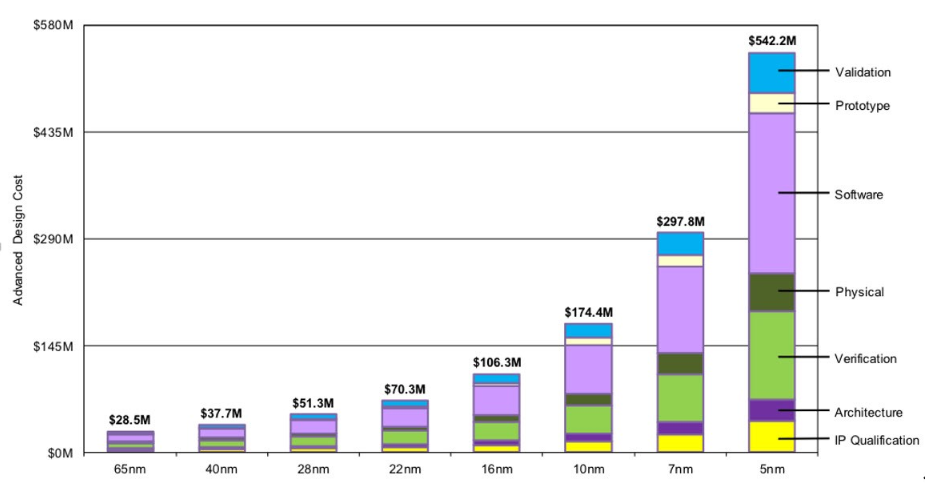

这种状态极大地影响了芯片设计的总体成本,并深刻地改变了设计验证方法。

图2:与工艺技术节点所对应的,设计最先进芯片的成本正在飙升。在28nm及以下,嵌入式软件验证和硬件验证部分的成本最高。来源:IBS

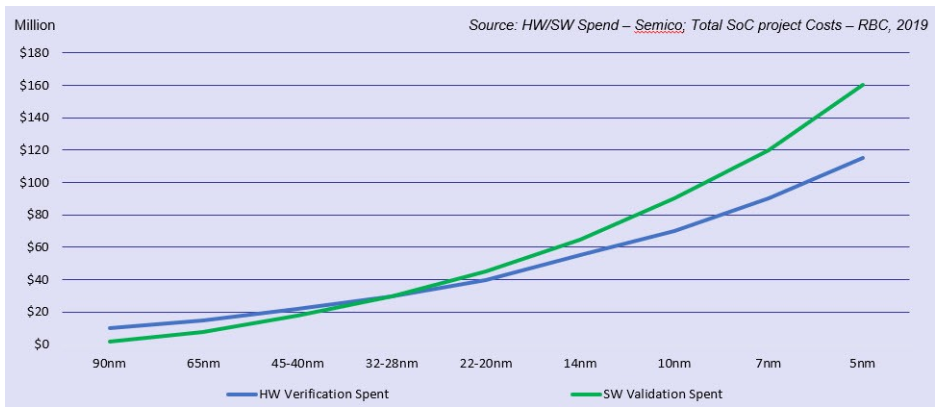

图4显示了每个过程技术节点在硬件验证和软件验证方面的花费,其中软件验证开销已经超过了硬件验证开销。

图3:由于工艺技术节点变小,硬件验证和软件验证的年度预算正在增长。

新的验证/验证要求:数十亿门的万亿次循环

半导体设计领域中的变化影响了设计验证方法,尤其是HDL Simulation,它的吞吐量已经突破天际。考虑下超10亿门的设计中,对硬件和嵌入式软件进行详尽的验证需要什么。

嵌入式软件包括驱动程序、一个或多个操作系统、中间件和应用程序。所有这些都与硬件交互。任何一种情况下的任何异常都会影响到整体,从而使验证/验证团队本已十分艰巨的任务更加恶化。挖掘深层次的错误,无论是硬件还是软件,都需要将其结果进行充分验证。

今天,验证团队必须处理另一项任务。为了在竞争激烈的环境中取胜,新设计必须在提供高性能和低功耗方面优于竞争对手。这两个目标都必须在开发阶段得到验证,然后才能进行设计。

实际上,这意味着需要在十亿个测试中的门设计(DUT)上处理数万亿个验证周期。无论其复杂性如何,任何测试台都无法实现该目标。它只能通过处理真实的应用程序或实际的工作负载基准来满足。

结论

只有硬件辅助验证工具(如硬件仿真器和FPGA原型)才具有引导操作系统和执行验证、仿真和分析DUT所需的整个软件堆栈的吞吐量。

值得注意的是,模拟器和FPGA原型的总拥有成本(COO)明显高于HDL Simulation的COO,这也解释了为什么2018年其收入超过了HDL Simulation的收入。撇开不谈,芯片设计验证小组也必须依靠仿真器和FPGA原型来实现他们的目标。因此,这一趋势将持续下去。

- 西门子推出 HEEDS AI Simulation Predictor 和 Simcenter Reduced Order Modeling 解决方案

- dSPACE开发高性能仿真环境 用于验证自动驾驶汽车传感器系统

- Multiphysics Simulation助力解决日益复杂的设计问题

- 实时&非实时综合应用在多个信号的测量

- e 络盟宣布Metcal焊接台将采用 Connection Validation™技术

- Cadence 发布 Verisium AI-Driven Verification Platform 引领验证效率革命

- Mentor Graphics Verification Academy 新增 SystemVerilog 课程和模式库

- Synopsys发布Verification Compiler验证编译器

- S2C Verification Module演示视频

- S2C 日前宣布其Verification Module技术(专利申请中)已可用于其基于Xilinx的FPGA原型验证系统中。V6 T

- 创实技术electronica 2024首秀:加速国内分销商海外拓展之路

- 欧洲三大芯片巨头,重新审视供应链

- 一场IC设计业盛宴!10场论坛 200位演讲嘉宾,300+展商亮相2万平米专业展会!

- 富昌电子于杭州举办技术日活动,聚焦新能源“芯”机遇

- 消息称铠侠最快明天获上市批准,市值有望达 7500 亿日元

- 美国政府敲定对格芯 15 亿美元《CHIPS》法案补贴,支持后者提升在美产能

- SK 海力士宣布量产全球最高的 321 层 1Tb TLC 4D NAND 闪存,计划 2025 上半年对外出货

- 三星电子 NRD-K 半导体研发综合体进机,将导入 ASML High NA EUV 光刻设备

- 芯片大混战将启:高通、联发科涉足笔记本,AMD 被曝入局手机