传统的字符叠加都是使用专用的OSD芯片,一般价格较高,而且通常只能实现英文字母和数字的叠加,使用不灵活,还要占用较多的PCB板空间,故障率也较高。

这里介绍的字符叠加方案是基于TI的2000系列DSP的,经过调试验证效果良好。

TMS320F2812是TI新近推出的高性能定点DSP,内部集成的EV模块使它很适用于高性能的电机控制应用场合。如要求高精度、高速的云台和机床等。以云台为例,通常需要随着电机的运转显示角度、坐标、距离等信息,以及一些简单的控制菜单,甚至可能要叠加简单的地图。用通常的OSD芯片根本无法完成如此复杂的涉及任意图形的叠加。而该叠加方案巧妙利用了2812的内部资源――SPI串口模块,实现了这些内容的叠加。

叠加原理:

图形叠加是把视频信号的每一行虚拟分成H个点,垂直分为V行,叠加图像就是H×V分辨率的单色位图。利用视频信号提取出的复合同步信号及场同步信号,确定叠加图像的有效点(即需要覆盖掉原视频图像的点),在这些点把视频信号切换到一个固定电平(可以由DSP控制)即可实现视频叠加。

方案实现:

该功能模块主要由四部分组成:复合视频信号交流耦合及直流恢复、视频同步信自成提取、视频叠加灰度控制、视频切换叠加。下面对各部分及软件实现做简要的描述。

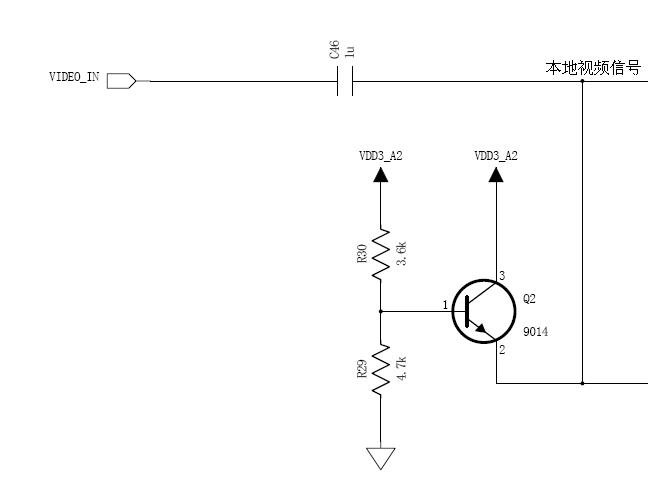

1) 复合视频信号交流耦合及直流恢复

视频信号交流耦合可以对前后级形成有效的隔离以起到很好的保护作用。但交流耦合后的复合视频信号会丢掉原信号的直流分量,导致丢失一部分背景亮度信息。而交流耦合带来的最严重的问题是:信号直流成分的丢失会导致同步头的上下漂移,使信号同步信息丢失。

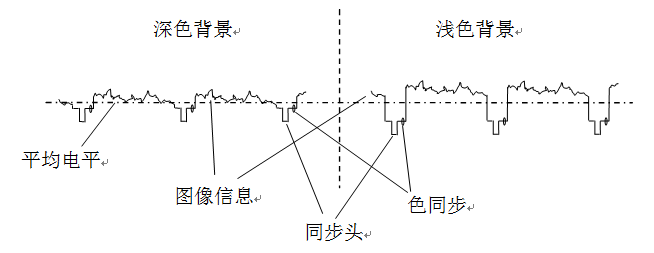

图1交流耦合视频信号示意图

从图1可以看到交流耦合后的信号是趋于平均电平对齐的,对不同亮度背景的信号,同步头电平差异很大,无法通过与一个固定的参考电平进行比较来提取同步信息。

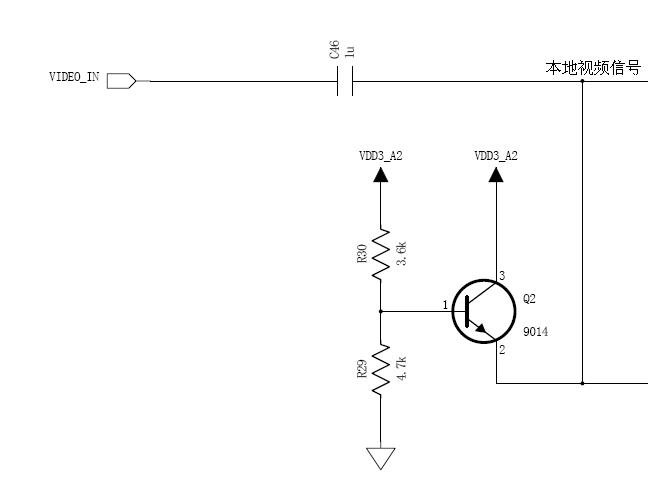

于是需要对信号进行直流恢复,这里采用三极管钳位电路(图2)。三极管钳位电路具有成本低、控制灵活、响应速度快等优点。这里钳位电路起到的作用就是将视频信号的低电平自动(即同步信号)对齐。为使峰值1V的视频信号比较适合后续3.3V供电系统作处理,将视频信号的低电平设置为1.1V(高电平为2.1V,相对3.3V电源,上下均有1.1V左右的电平裕量),于是R29与R30分压为1.1V+0.7V=1.8V。由此确定R29与R30值分别为4.7K和3.6K。

图2直流恢复-钳位电路

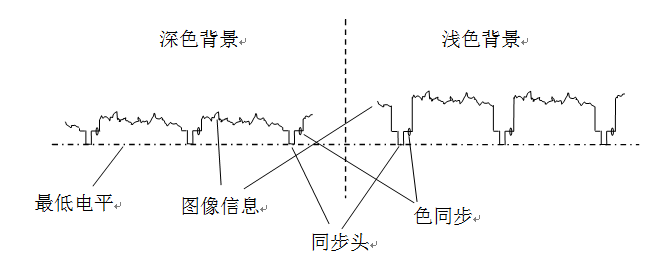

恢复后的视频图像如图所3示:

图3直流恢复后的视频信号示意图

这样便完成了视频信号的直流恢复。可以很容易的用简单比较器电路提取同步信息。另外,采用钳位电路的另一个好处是,75欧负载是在耦合电容前面,耦合电容后面的本地视频信号所在的网络阻抗很大(约30K),只需要1uF的磁片电容就可以实现视频信号的良好耦合――有效带宽与75欧电阻配400uF电解电容相当。这就大大缩小了耦合电容的体积,并提高了电容寿命。

2) 视频同步信号提取

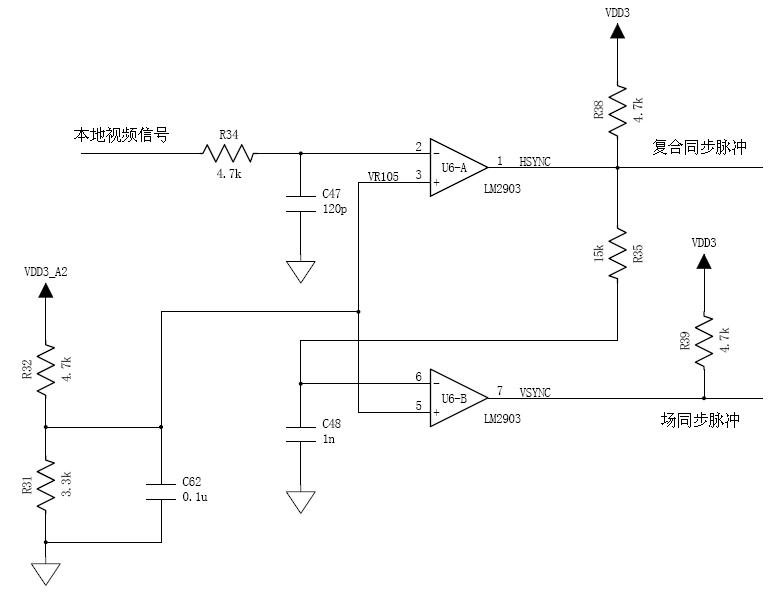

复合同步主要用于行同步,比较容易提取,只需要一个简单的积分滤掉高频杂波,然后经过一个比较电路就能得到。传统的场视频信号提取是利用滤波和微分电路实现的,那种方式不容易实现场同步信号与复合同步信号的严格对齐,会造成叠加内容的上下抖动。这里使用了一种其它的方法――利用前面得到的复合同步脉冲里的槽脉冲经过一点简单的处理即可得到场同步信号。因为槽脉冲的宽度为29.65us,而行同步头宽度只有4.7us。所以用一个积分电路和一个比较电路就能由复合同步信号提取出场同步信号――图4的R35和C48就是该积分电路,时间常数取介于4.7us与29.65us之间的15us(时间裕量较大),于是取值分别为15K与1nF。另外,通过计算还找到一个合适的值,使场同步信号提取与复合同步信号提取使用同一个参考电平以减少元器件。提取的同步脉冲直接送到2812的中断输入引脚。图4为同步信号提取电路图:

图4同步脉冲提取电路

比较器不需要速度很快,只需延迟时间一致就可以,于是采用低成本的双路比较器LM2903。

3) 视频叠加灰度控制

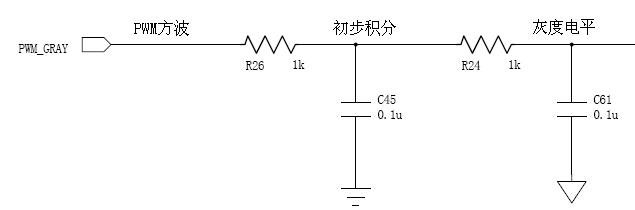

图5叠加灰度控制电路

视频叠加是通过快速在视频图像与灰度电平之间切换实现的。图像背景不同,往往需要改变叠加内容的灰度才能达到理想的视觉效果。于是利用2812剩余的一路PWM信号积分后代替DA来产生灰度电平(两个电机控制使用4个PWM脚,还剩余2个)。初步积分地需选用前面的数字地,以保障流畅的PWM信号回路(数字部分)。对1MHz的PWM信号,可以取R26、C45的值为1K与0.1uF,使输出纹波低于5mV。然后再经过一级针对模拟地的RC滤波,使输出灰度电平纹波达到uV级。

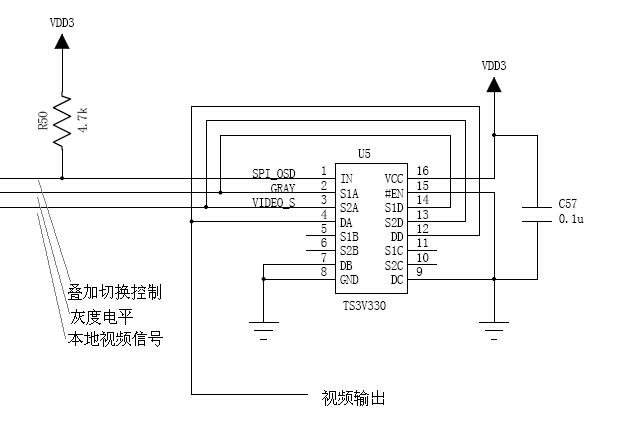

4) 视频切换叠加

叠加通过一个视频切换芯片来实现,为减少原视频信号失真,选用TI的带宽达300MHz的视频切换芯片TS3V330,并且使用两路并连以提高导通电阻的一致性。该芯片通道切换时间低于10ns,可以很好的满足应用需求。具体电路如下图6所示:

图6切换叠加电路

叠加功能中视频信号与固定电平的切换是通过DSP自带的SPI口完成的。2812的SPI最大传输比特率为37.5Mb/s,并且SPI模块自带16级16位的FIFO。这里显示水平分辨率H刚好可以取256,可以满足一般显示应用需求,而且刚好能利用SPI模块的FIFO实现每行仅进行一次SPI写操作,极大的减少了CPU占用时间。DSP每次检测到复合同步脉冲触发的硬件中断,进行一次对SPI FIFO写的操作,检测到场同步中断即进行行数清0的操作。按照每64us进入中断进行一次16字(16bit*16)的搬移计算,CPU占用量不及1%。

垂直分辨率V取256,奇偶场不需区分――也就是相邻帧的同一行叠加内容相同,这样在满足应用需求的前提下可以减少奇偶场判断所需的软件资源。对PAL制和NTSC制信号,可以取V的一部分,即有效叠加内容少于256行。

我们采用的DSP(TMS320F2812)内带128k×16bit的FLASH和18k×16bit的RAM。利用64k的FLASH装载一级汉字库及ASC字形库和一个4k的自定义LOGO或其它图形。其余64k装载程序。为减少字符叠加及叠加内容维护占用DSP的计算量,给字符叠加专门分配一块4k×16bit的RAM作为OSD缓存。只有叠加内容需要更改的时候才对RAM内容进行写操作。

5) 软件部分

该方案所需的软件涉及的内容较少也比较简单。主要是两个中断函数,里面执行一些简单的行数处理和对SPI FIFO的写操作。另外还涉及一些字符处理的子函数,如在某个位置叠加/清除一个字符以及满屏图像叠加和清屏等。这些子函数是对RAM内图形缓冲进行写操作,对实时性要求很低,管理起来也很方便。

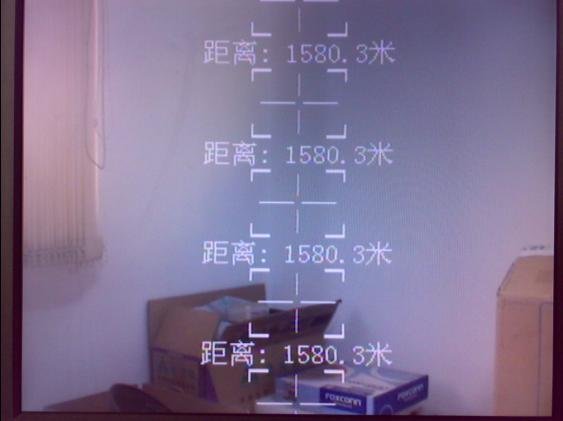

项目结述:

目前该方案的软硬件都已经实现,占用DSP资源少,效果良好,字符稳定。不会影响电机控制,DSP还有非常大的计算裕量。单字符及图形叠加模块增加的成本只有不足5RMB,极大限度的利用了2812的剩余资源。该方案也可修改后用低成本的单片机实现。

图7最终叠加效果图