历史上的今天

今天是:2025年02月17日(星期一)

2020年02月17日 | 解析3D IC的技术和发展

2020-02-17 来源:SiP系统级封装技术

从SiP系统级封装的传统意义上来讲,凡是有芯片堆叠的都可以称之为3D,因为在Z轴上有了功能和信号的延伸,无论此堆叠是位于IC内部还是IC外部。但是目前,随着技术的发展,3D IC却有了其更新、更独特的含义。

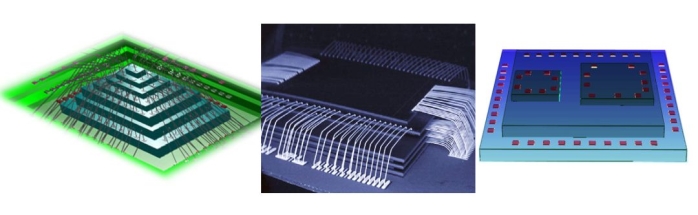

基于芯片堆叠式的3D技术

3D IC的初期型态,目前仍广泛应用于SiP领域,是将功能相同的裸芯片从下至上堆在一起,形成3D堆叠,再由两侧的键合线连接,最后以系统级封装(System-in-Package,SiP)的外观呈现。堆叠的方式可为金字塔形、悬臂形、并排堆叠等多种方式,参看下图。 另一种常见的方式是将一颗倒装焊(flip-chip)裸芯片安装在SiP基板上,另外一颗裸芯片以键合的方式安装在其上方,如下图所示,这种3D解决方案在手机中比较常用。

另一种常见的方式是将一颗倒装焊(flip-chip)裸芯片安装在SiP基板上,另外一颗裸芯片以键合的方式安装在其上方,如下图所示,这种3D解决方案在手机中比较常用。

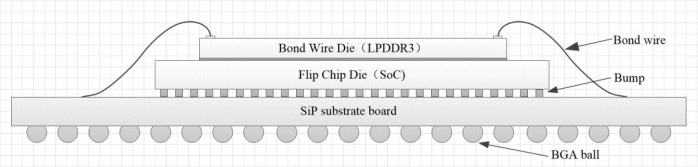

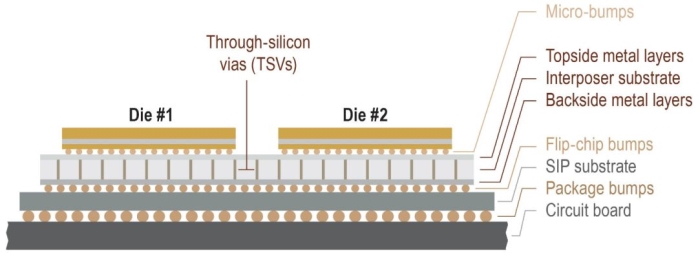

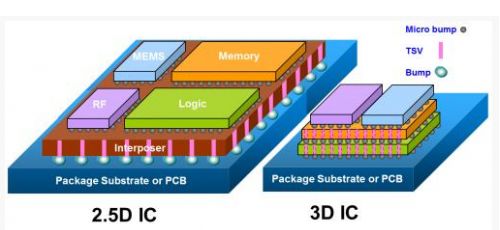

基于无源TSV的3D技术

在SiP基板与裸芯片之间放置一个中介层(interposer)硅基板,中介层具备硅通孔(TSV),通过TSV连结硅基板上方与下方表面的金属层。有人将这种技术称为2.5D,因为作为中介层的硅基板是无源被动元件,TSV硅通孔并没有打在芯片本身上。如下图所示:

基于有源TSV的3D技术

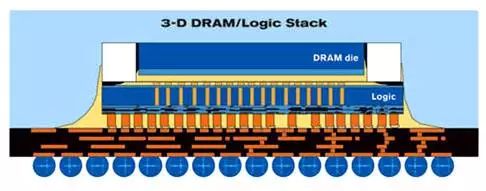

在这种3D集成技术中,至少有一颗裸芯片与另一颗裸芯片叠放在一起,下方的那颗裸芯片是采用TSV技术,通过TSV让上方的裸芯片与下方裸芯片、SiP基板通讯。如下图所示:

下图显示了无源TSV和有源TSV分别对应的2.5D和3D技术。

以上的技术都是指在芯片工艺制作完成后,再进行堆叠形成3D,其实并不能称为真正的3D IC 技术。

这些手段基本都是在封装阶段进行,我们可以称之为3D集成、3D封装或者3D SiP技术。

基于芯片制程的3D技术

![]()

![]()

![]()

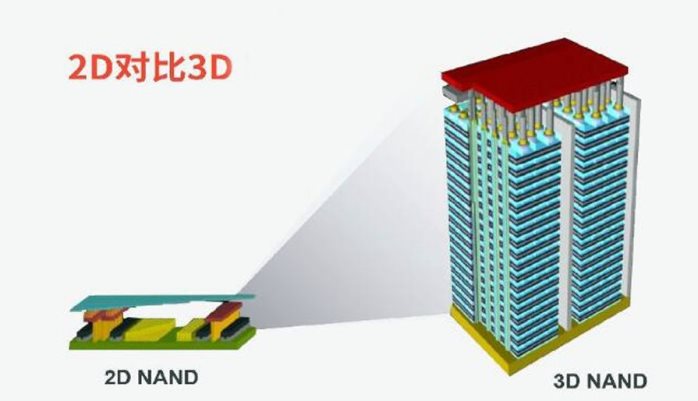

目前,基于芯片制造的3D技术主要应用于3D NAND FLASH上。

东芝和三星在 3D NAND 上的开拓性工作带来了两大主要的 3D NAND 技术。

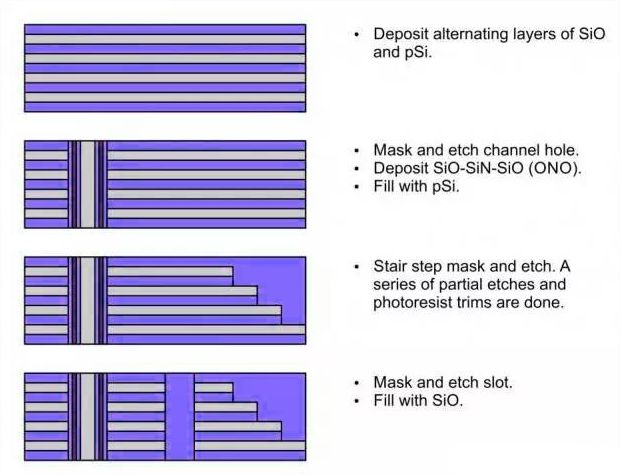

东芝开发了 Bit Cost Scalable(BiCS)的工艺。BiCS 工艺采用了一种先栅极方法(gate-first approach),这是通过交替沉积氧化物(SiO)层和多晶硅(pSi)层实现的。然后在这个层堆叠中形成一个通道孔,并填充氧化物-氮化物-氧化物(ONO)和 pSi。然后沉积光刻胶,通过一个连续的蚀刻流程,光刻胶修整并蚀刻出一个阶梯,形成互连。最后再蚀刻出一个槽并填充氧化物。如下图所示。

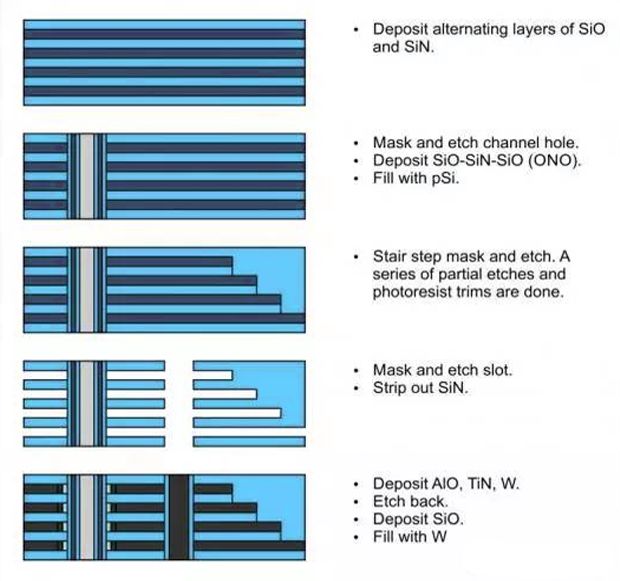

三星则开发了 Terabit Cell Array Transistor (TCAT)工艺。TCAT 是一种后栅极方法( gate-last approach),其沉积的是交替的氧化物和氮化物层。然后形成一个穿过这些层的通道并填充 ONO 和 pSi。然后与 BiCS 工艺类似形成阶梯。最后,蚀刻一个穿过这些层的槽并去除其中的氮化物,然后沉积氧化铝(AlO)、氮化钛(TiN)和钨(W)又对其进行回蚀(etch back),最后用坞填充这个槽。如下图所示。

3D NAND目前已经能做到64层甚至更高,其产量正在超越 2D NAND,而且随着层数的进一步扩展,3D NAND还能继续将摩尔定律很好地延续。

目前应用在IC制造上的3D技术也仅限于NAND FLASH,随着技术的发展,应该很快也会应用到其它的IC领域,那时候,真正的3D IC时代就到来了!

史海拾趣

|

请问一个安装arm-elf-tools-20030314的问题 我在安装的时候,先碰到一个问题是 tail: cannot open `+43\' for reading: No such file or directory 网上搜索了一下,普遍的解决方法是:找到arm-elf-tools-20040427.sh文件的第39行, tail +${SKIP} ${SCRIPT} ¦ gunzip ¦ tar xvf ...… 查看全部问答> |

|

今天耍了个很好玩的功能,按键控制app中方框的转动,我把代码修改到了每按一次用户键,方块就会X,Y,Z一起转动,很好玩的功能 修改的代码如下 方块转动的图片: … 查看全部问答> |

|

EEWORLD大学堂----TI SimpleLink轻松、快捷的无线解决方案 TI SimpleLink轻松、快捷的无线解决方案:https://training.eeworld.com.cn/course/396… 查看全部问答> |