历史上的今天

今天是:2025年03月10日(星期一)

2021年03月10日 | 深度解析STM32单片机JTAG的复用方法

2021-03-10 来源:eefocus

先来copy下 JTAG、SW接口的定义

JTAG:JTAG(JointTest Action Group;联合测试工作组)是一种国际标准测试协议,主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

SWD:SW(Serial Wire Mode Interface),串行接口线模式。在串行线模式,只有针TCLK和TMS使用。TDO数据输出引脚是一个可选。

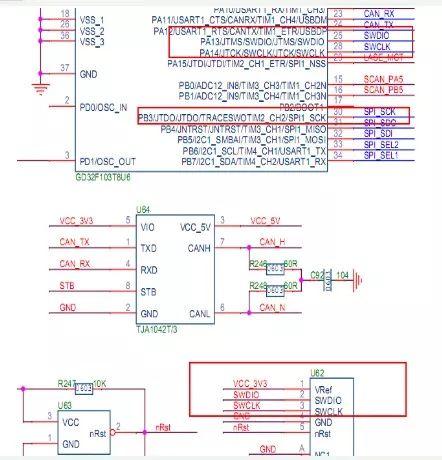

SWD下载调试 原理图:

从图中看到:板子使用SWD接口下载调试,即使用SWDIO、SWCLK(PA13、PA14);PB3–JTDO 默认功能为JTAG的,而这里用作其他的功能–普通I/O。

问题来了:

1、需要关掉PB3的JTAG功能,复用为其他功能。

2、SWD 和传统的调试方式区别。

STM32JTAG复用相关方法 :

直接上代码,如下:

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOB|RCC_APB2Periph_AFIO,ENABLE);//改变指定管脚的映射GPIO_Remap_SWJ_JTAGDisableJTAG-DP失能+SW-DP使能GPIO_PinRemapConfig(GPIO_Remap_SWJ_JTAGDisable,ENABLE);。..。...12345

但,当设置了以上语句后,当运行了这两个语句后,JTAG仿真就与目标失去去联系。

解决办法有:

1、设置启动模式为ISP模式(BOOT0=1、BOOT1=0)或设置启动模式为RAM运行模式(BOOT0=1、BOOT1=1)。 将开发板断电后重新上电,此时就因不是在用户程序模式,因此就不会执行禁用JTAG的语句,JTAG功能也就可以正常使用。

2、设置启动模式为ISP模式(BOOT0=1、BOOT1=0),用ISP程序将STM32的FLASH擦除,之后就可恢复JTAG功能。

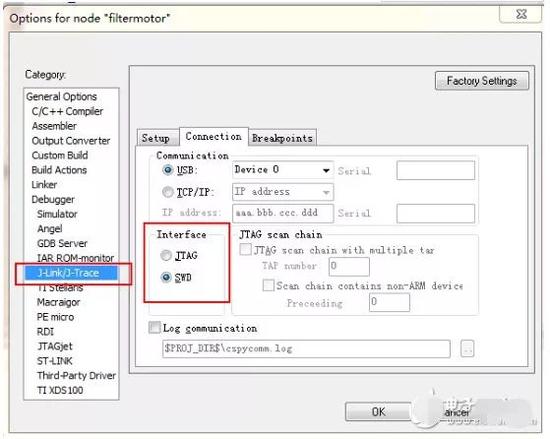

3、如果你的仿真器支持SWD仿真模式,如IAR下用JLINK、MDK下用ULINK2。 直接将仿真器的模式设为SWD模,就可以不受这个禁止JTAG功能的影响了。

我的环境切合第三个解决方案,IAR设置如下:

SWD 和传统的调试方式区别 :

SWD 模式比 JTAG 在高速模式下面更加可靠。 在大数据量的情况下面 JTAG 下载程序会失败, 但是 SWD 发生的几率会小很多。基本使用 JTAG 仿真模式的情况下是可以直接使用 SWD 模式的, 只要你的仿真器支持。 所以推荐大家使用这个模式。

在大家 GPIO 刚好缺一个的时候, 可以使用 SWD 仿真, 这种模式支持更少的引脚。

在大家板子的体积有限的时候推荐使用 SWD 模式, 它需要的引脚少, 当然需要的 PCB 空间就小啦! 比如你可以选择一个很小的 2.54 间距的 5 芯端子做仿真接口。

史海拾趣

|

在科学技术的进步和人们对移动通信服务需求的双重推动下,楼宇门禁对讲系统正应用到各小区中。目前楼宇门禁对讲移动通信网络仍将继续不断地向前发展,以后将能更完美地实现广大楼宇对讲移动通信用户的通信服务需求。 无线接口中的不安全因素 &nbs ...… 查看全部问答> |

|

如何检验“ADC转换后的数据通过UART传送时是否遗漏”,请教 大家好,小弟最近在用ADI公司的ADuC7060芯片,要实现ADC转换后的数据通过UART传送到超级终端。 CPU是32位,ADC精度为24位。 我程序的总体思路是,ADC连续转换模式,每转换完一组24位数据,就触发中断,随后交给UART发送。(我现在的UART波特率大 ...… 查看全部问答> |

|

dwRet=RasDial(NULL,NULL,&RasDialParams,0xFFFFFFFF,this->m_hWnd,&m_hRasConn); 拨号,第五个参数为NULL是阻塞拨号成功。现在想实现异步的方式,工程是基于对话框的,所以hWnd句柄直接用this->m_hWnd // 注册WM_RASDIALEVENT消息 ...… 查看全部问答> |

|

组成原理的一道题,不明白为什么要加一个门电路,麻烦讲解一下,谢谢! CPU的地址总线16根(A15—A0,A0为低位),双向数据总线8根(D7—D0),控制总线中与主存有 关的信号有MREQ(允许访存, 低电平有效),R/W(高电平为读命令,低电平为写命令)。主存地址空间分 配如下:0—8191为系统程序区,由只读存储芯片组成;8192— ...… 查看全部问答> |

|

PXA270核心板方案: CPU:PXA270 SDRAM:128M FLASH:32M 接口:USB、SDCARD、SERIAL等 LCD+TOUCH:3.5‘ 支持WIFI 方案可提供:SCH + PCB + BOOM + WINCE ...… 查看全部问答> |

|

小弟采用的是ixp425的cpu,vxworks操作系统。使用两个通用定时器,实现优先级高定的时器中断打断优先级低的定时器中断服务程序,而优先级低的不能打断高优先级的中断。 但是小弟做的试验结果是两个定时器中断没有相互打断:任何一个进入中断服务程 ...… 查看全部问答> |

|

板子跑的linux,我在调spi的时候遇到一个问题就是读写外设的寄存器的时间开销太大。 static void transfer (int fd) { int ret; uint8_t tx[] = { 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, ...… 查看全部问答> |

|

首先说这个电路是正常运行的,UC2844内部的误差放大器反相端直接接地,反馈直接接到了误差放大器的输出,常规的这种用法都是在COMP端加一个类似上拉电阻的形式,然后与光耦的副边串联,通过控制分压的值来反馈到COMP端,而这里是直接连到光耦的副边 ...… 查看全部问答> |