历史上的今天

今天是:2024年12月07日(星期六)

2021年12月07日 | 第十八章:Android LCD(四):LCD驱动调试篇

2021-12-07 来源:eefocus

关键词:android LCD TFTSN75LVDS83B TTL-LVDS LCD电压背光电压

平台信息:

内核:linux2.6/linux3.0

系统:android/android4.0

平台:samsung exynos 4210、exynos 4412 、exynos 5250

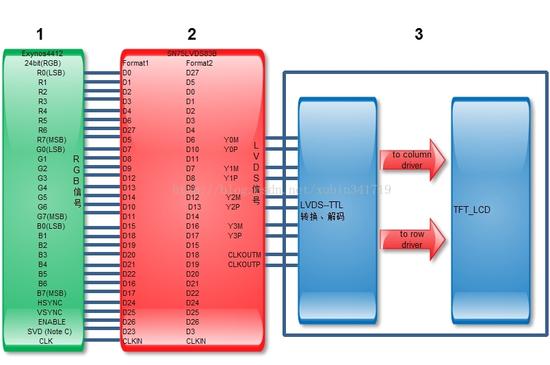

这篇我们以一个实例来说明,Samsung Exynos4412搭配TTL转LVDS芯片SN75LVDS83B、LVDS接口LCD为例说明。从硬件接口、驱动配置、背光PWM调节三部分说明。

一、LCD接口原理以及硬件电路

Samsung Exynos4412、SN75LVDS83B、LVDS接口LCD(24bit)为例说明,三者的关系如下:

如上图所示,我们在应用中我,主控(Exynos4412)输出RGB信号到TFT-LCD大体经过三部分:

(1)、标号1部分,主控(Exynos4412)输出TTL信号;

(2)、标号2部分,TTL(RGB)-LVDS转换芯片SN75LVDS83B,把TTL信号转换成LVDS信号,传输到显示器的LVDS接收端;这部分有SN75LVDS83B编码芯片自动完成,所以我们不需要程序控制;

(3)、标号3部分,分两个小部分,LVDS转换成TTL,TFT-LCD显示部分;我们前面说过,TFT-LCD其实只识别TTL信号,所以要有一个转换的过程,先把LVDS信号转换、解码成TTL信号,在TFT-LCD上显示。

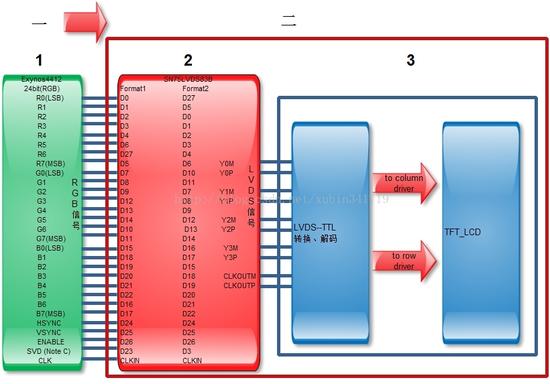

有上面的过程,其实我们关心调试的部分只有标号1部分到标号2部分,后面标号2到标号3的部分是自动完成的,不需要我们程序上控制,把标号2部分、标号3部分合并:

标号二部分可以理解为一个TTL(RGB)接口的LCD,如下图所示,标号一部分就是主控信号输出端,简化图如下所示:

其实最简单的做法就是找个TTL接口的TFT-LCD,这样直接接上就可以。下面我们看下硬件上的电路连接:这个和我们上篇用的相同。

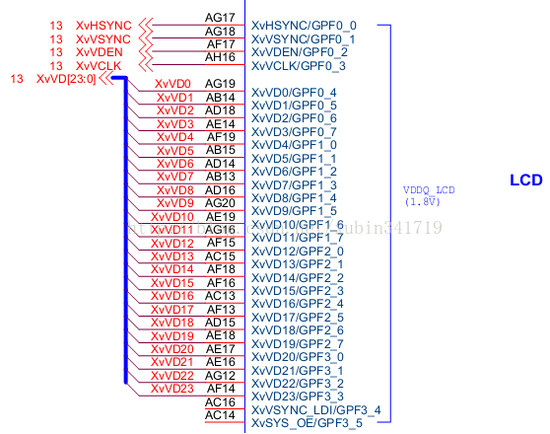

有上面图可以看出:硬件连接

网络标号 | 说明 | 管脚 |

XvVD[0:23] XvVDEN XvVSYNC XvHSYNC XvVCLK | RGB数据、使能、行场同步、时钟信号 | 这是TTL信号输出 |

LCD_PWM | 调节背光 | XpwmTOUT1/LCD_PWM/GPD0_1 |

LCD_LED_EN | LCD电压(TFT电压)使能 | GPC1_2 |

LED_BL_EN | LED背光使能 | GPL2_4 |

上面可分为几部分,电路连接部分分析:

(1)、TTL数据部分

这张图有木有烂掉呀,哈哈,就是这些数据了。还有有木有想起来摄像头的数据(ITU接口)也是这样的??其实视频这种信号的原理是通用的,所以LCD通了,摄像头也就知道怎么回事了。

(2)、PWM背光调节

PWM其实也是芯片的一个功能模块,看到他的管脚就是一个复用脚XpwmTOUT1/LCD_PWM/GPD0_1。上一篇我们粗略的了解了PWM,就是用到这里。但是有一个疑问,PWM是调节背光电压的,背光电压一般都是12V以上的,我们PWM只有0-3V的样子,Exynos4412的IO只有1.8V。怎么调节电压???

其实这个PWM只是给LCD上PWM控制部分,真正的电压还是通过LCD控制板上的电路实现。

( 3 )、 LED 背光、 LCD 电压控制a 、背光:LED+

我们可以看到这个升压电路,通过 SY7208 把 VBATT 升压到 18V ,供给 LED 背光。 SY7208 最大升压 26V 。这个电压是提供给我们前面讲的背光的,也就是 CCFL 灯管或者 LED 背光组的电压。

b、LCD电压

这个电压也就是给你我们TFT阵列组用的,控制LCD液晶元素。

这部分电路分析完成,我们就有比较清晰的思路出,要一个LCD工作,要完成两部分内容:LCD上电控制,背光、LCD电压;信号输出。

二、LCD 驱动部分调试

LCD这部分,像上篇我们说的frambuffer这些部分一般平台都是可以用的,除非你是芯片厂的要写这部分。一般公司拿到的demo板子这部分都是通的,只是针对自己的lCD换一些参数。

下面我们针对三星平台我们调试LCD的时时候程序方面的改动:

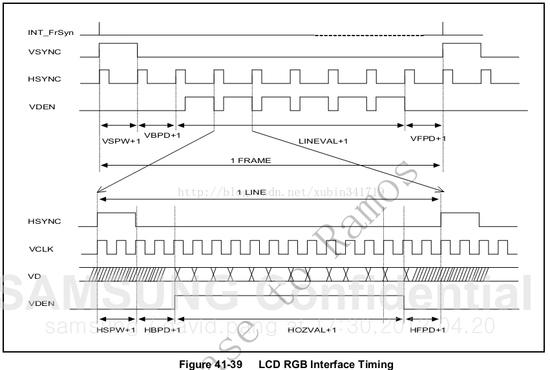

1、屏参数的配置

/kernel/drivers/video/Samsung/s3cfb_wa101s.c

static struct s3cfb_lcd wa101 = {

.width = 1280,//LCD 分辨率宽1280

.height = 800, //LCD 分辨率高 800

.bpp = 24,//CLD 数据位 24bit

.freq = 60,//LCD 像素时钟 60MHz

.timing = {//LCD porch无效值

.h_fp = 70,

.h_bp = 70,

.h_sw = 20,

.v_fp = 10,

.v_fpe = 0,

.v_bp = 10,

.v_bpe = 0,

.v_sw = 3,

},

.polarity = {//时钟、行场的极性;

.rise_vclk = 1,

.inv_hsync = 1,

.inv_vsync = 1,

.inv_vden = 0,

},

};

/* name should be fixed as 's3cfb_set_lcd_info' */

void s3cfb_set_lcd_info(struct s3cfb_global *ctrl)//初始化结构体

{

wa101.init_ldi = NULL;

ctrl->lcd = &wa101;

#endif

}

还能想起上一篇的如何阅读规格书中的那些参数不,把这些填入就可以。

2、数据管脚初始化

kernel/arch/arm/mach-exynos/setup-fb-s5p.c

void s3cfb_cfg_gpio(struct platform_device *pdev)

{

s3cfb_gpio_setup_24bpp(EXYNOS4_GPF0(0), 8, S3C_GPIO_SFN(2), S5P_GPIO_DRVSTR_LV4);

s3cfb_gpio_setup_24bpp(EXYNOS4_GPF1(0), 8, S3C_GPIO_SFN(2), S5P_GPIO_DRVSTR_LV4);

s3cfb_gpio_setup_24bpp(EXYNOS4_GPF2(0), 8, S3C_GPIO_SFN(2), S5P_GPIO_DRVSTR_LV4);

s3cfb_gpio_setup_24bpp(EXYNOS4_GPF3(0), 4, S3C_GPIO_SFN(2), S5P_GPIO_DRVSTR_LV4);

}

LCD 数据脚初始化,驱动能力设为最高 S5P_GPIO_DRVSTR_LV4 ;管脚驱动能力, S5P_GPIO_DRVSTR_LV1-4 四个等级选择。3、 时钟控制部分

kernel/arch/arm/mach-exynos/setup-fb-s5p.c

int s3cfb_clk_on(struct platform_device *pdev, struct clk **s3cfb_clk)

{

struct clk *sclk = NULL;

struct clk *mout_mpll = NULL;

struct clk *lcd_clk = NULL;

u32 rate = 0;

int ret = 0;

lcd_clk = clk_get(&pdev->dev, "lcd");

if (IS_ERR(lcd_clk)) {

dev_err(&pdev->dev, "failed to get operation clk for fimdn");

goto err_clk0;

}

ret = clk_enable(lcd_clk);

if (ret < 0) {

dev_err(&pdev->dev, "failed to clk_enable of lcd clk for fimdn");

goto err_clk0;

}

clk_put(lcd_clk);

sclk = clk_get(&pdev->dev, "sclk_fimd");

if (IS_ERR(sclk)) {

dev_err(&pdev->dev, "failed to get sclk for fimdn");

goto err_clk1;

}

if (soc_is_exynos4210())

mout_mpll = clk_get(&pdev->dev, "mout_mpll");

else

mout_mpll = clk_get(&pdev->dev, "mout_mpll_user");

if (IS_ERR(mout_mpll)) {

dev_err(&pdev->dev, "failed to get mout_mpll for fimdn");

goto err_clk2;

}

ret = clk_set_parent(sclk, mout_mpll);

if (ret < 0) {

dev_err(&pdev->dev, "failed to clk_set_parent for fimdn");

goto err_clk2;

}

if ((soc_is_exynos4412()) && (samsung_rev() >= EXYNOS4412_REV_2_0))

ret = clk_set_rate(sclk, 880000000);

else

ret = clk_set_rate(sclk, 800000000);

if (ret < 0) {

dev_err(&pdev->dev, "failed to clk_set_rate of sclk for fimdn");

goto err_clk2;

}

dev_dbg(&pdev->dev, "set fimd sclk rate to %dn", rate);

clk_put(mout_mpll);

ret = clk_enable(sclk);

if (ret < 0) {

dev_err(&pdev->dev, "failed to clk_enable of sclk for fimdn");

goto err_clk2;

}

*s3cfb_clk = sclk;

return 0;

err_clk2:

clk_put(mout_mpll);

err_clk1:

clk_put(sclk);

err_clk0:

clk_put(lcd_clk);

史海拾趣

|

新手请教verilog实现VGA显示移动小球的问题:使用ALTER公司的QuartusII软件开发,小弟现在想要实现一个用字模实现的小球,在屏幕上斜线移动的问题,但球会逐行显示又逐行消失,若只横向移动,则能一直显示,希望大家不吝赐教,部分代码如下: modu ...… 查看全部问答> |

|

根据时序要求,我们设定VM/VDEN信号作LCD的ENAB信号,VCLK信号作LCD的NCLK信号。要想得到合适的VM和VCLK波形,就要正确设定寄存器的值,根据寄存器的值与VM和VCLK波形的关系,我们设定了如下关键寄存器的值: HSPW=10;HBPD=100;HFPD=47; VSPW=1;VBPD=37 ...… 查看全部问答> |

|

1PG的#18#17位置设置(1)的设置范围是“0到正负999999”,如果我的伺服驱动器设定每转输入100000个脉冲,那么我能让电机旋转的圈数最多只有9圈多?比如我要电机转15圈,那么每转脉冲数乘以旋转圈数(100000*15=1500000)就超出了设定范围了!如果 ...… 查看全部问答> |

|

一、做个电子负载 板子早就打好了,这10块板一直在睡着,没有动 这次准备使用C2000 LaunchPad把它做起来。 二、做个数字电源 原来使用F28035做的BUCK部分,性能不错。这次使用F28027来做,只做BUCK型降压的电源。 PCB还没有做,或者使用试 ...… 查看全部问答> |

|

EPwm1Regs.TBPRD = 5000; EPwm1Regs.TBPHS.half.TBPHS = 0; EPwm1Regs.TBCTR = 0; EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; &n ...… 查看全部问答> |