历史上的今天

今天是:2025年12月07日(星期日)

2022年12月07日 | s3c2440时钟频率设置

2022-12-07 来源:zhihu

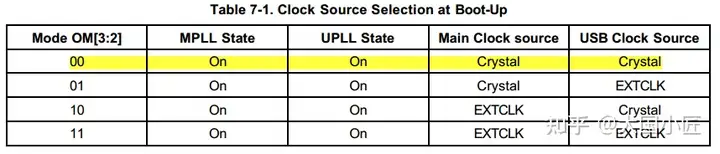

时钟源选择

在nRESET的上升沿锁存OM[3:2]引脚,两个引脚在原理图中都接地,所以都为低电平。所以MPLL的时钟源来源于晶振;UPLL的时钟源也来源于晶振。

2. 配置流程

t1时刻:上电后,晶振起振,FCLK直接由晶振产生;

t2时刻:nRESET拉高,OM[3:2]被所存,晶振作为MPLL与UPLL的输入,但是由于MPLL与UPLL还未配置,所以FCLK还是工作于晶振时钟;

t3时刻:软件设置PLL CONTROL REGISTER (MPLLCON & UPLLCON)寄存器,配置MDIV、PDIV、SDIV的值,决定MPLL与UPLL的输出频率;紧接着设置CLOCK DIVIDER CONTROL (CLKDIVN)寄存器,配置FCLK/HCLK/PCLK之间的比例;这个时候PLL进入锁定状态;

t4时刻:锁定时间结束,PLL输出稳定。

史海拾趣

|

无线传输数据,发射端移动的时候,对传输质量影响很大,请问有没有什么好的解决方法? 现在有一个无线的项目(不采用跳频),我对无线接触不多,碰到这样的问题,发射端在移动的时候,对发射质量影响特别大,请教一下这方面的知识,和解决这个问题的方法。谢谢!… 查看全部问答> |

|

51的外部程序存储器地址在P0口和P2口上,所以必须有地址线与这些口相连啊,但是没有地址线的EEPRIOM呢>?还能做外扩程序存储器么? 只能做非易失性数据存储器了?… 查看全部问答> |

|

在脉冲RD的上升沿将内存的数据读到芯片的数据端口DOUT,怎样实现? 可以让这个脉冲信号直接做clock使用吗?? 例如下面这样写:always @(posedge RD ) DOUT_EN==1\'b1;产生一个enable 信号,综合时要对这个RD create clock 吗??… 查看全部问答> |

|

我现在有一个vxworks的系统,以前是在一个特殊的工控机上跑的,现在我想在虚拟机下跑。我的解决途径是重新生成一个bsp引导vxworks启动,但是vxworks启动后在初始化阶段出现错误,错误提示信息是output not supported width=1024 ,height=768,直觉 ...… 查看全部问答> |

|

MSP430驱动步进电机,使用DRV8814芯片原理图和参考源代码 TI DRV8814 步进电机驱动芯片:具有浪涌电流保护功能的 2.5A 双路刷式直流电机驱动器 DRV8814原理设计,MSP430与其接口电路原理图参见附件。 … 查看全部问答> |