历史上的今天

今天是:2025年12月12日(星期五)

2022年12月12日 | 51单片机管脚说明文档

2022-12-12 来源:zhihu

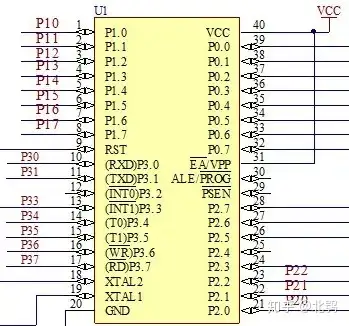

P0端口(P0.0-P0.7):P0口为一个8位漏极开路双向I/O口,每个引脚可吸收8TTL门电流。当P1口的管脚第一次写1时,被定义为高阻输入。P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。

P1端口(P1.0-P1.7):P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。P1口管脚写入1后,被内部上拉为高电平,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。在FLASH编程和校验时,P1口作为第八位地址接收。

P2端口(P2.0-P2.7):P2口为一个内部上拉电阻的8位双向I/O口,P2口缓冲器可接收,输出4个TTL门电流,当P2口被写“1”时,其管脚被内部上拉电阻拉高,且作为输入。并因此作为输入时,P2口的管脚被外部拉低,将输出电流。这是由于内部上拉的缘故。P2口,用于外部程序存储器或16位地址外部数据存储器进行存取时,P2口输出地址的高八位。在给出地址“1”时,它利用内部上拉优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器的内容。P2口在FLASH编程和校验时接收高八位地址信号和控制信号。

P3端口(P3.0-P3.7):P3口管脚是一个带有内部上拉电阻的8位的双向I/O端口,可接收输出4个TTL门电流。当P3口写入“1”后,它们被内部上拉为高电平,并用作输入。作为输入端时,由于外部下拉为低电平,P3口将输出电流(ILL)。P3口同时为闪烁编程和编程校验接收一些控制信号。

VCC(40):供电电压,其工作电压为5V。

GND(20):接地。

复位RST(9):复位输入。在振荡器运行时,有两个机器周期(24个振荡周期)以上的高电平出现在此引脚时,将使单片机复位,只要这个引脚保持高电平,51芯片便循环复位。复位后P3.0-P3.7口均置1,引脚表现为高电平,程序计数器和特殊功能寄存器SFR全部清零。当复位脚由高电平变为低电平时,芯片为ROM的00H处开始运行程序。复位操作不会对内部RAM有所影响。

ALE/PROG (30):当访问外部存储器时,地址锁存允许的输出电平用于锁存地址的地低位字节。在FLASH编程期间,此引脚用于输入编程脉冲。在平时,ALE端以不变的频率周期输出正脉冲信号,此频率为振荡器频率的1/6。因此它可用作对外部输出的脉冲或用于定时目的。然而要注意的是:每当用作外部数据存储器时,将跳过一个ALE脉冲。如果想禁止ALE的输出可在SFR8EH地址上置0。此时, ALE只有在执行MOVX,MOVC指令是ALE才起作用。另外,该引脚被略微拉高。如果微处理器在外部执行状态ALE禁止,则置位无效。

PSEN(29):外部程序存储器的选通信号。在由外部程序存储器取指令期间,每个机器周期两次PSEN有效。但在访问外部数据存储器时,这两次有效的PSEN信号将不出现。

XTAL1(19):来自反向振荡放大器的输入及内部时钟工作电路的输入。

XTAL2(18):来自反向振荡器的输出。

EA/VPP(31):当EA保持低电平时,则在此期间外部程序存储器(0000H-FFFFH),不管是否有内部程序存储器。注意加密方式1时,EA将内部锁定为RESET;当EA端保持高电平时,此间内部程序存储器。在FLASH编程期间,此引脚也用于施加12V的编程电源(VPP)。

上一篇:详解上拉电阻的定义,作用与选值

史海拾趣

|

机器人的手脚可以任720度任意转动,头部可360度转动,足球、篮球、棒球、橄榄球,他是样样精通。身高约15CM,摄像头像素130W。支持USB2.0,BIT24。 … 查看全部问答> |

|

被 几个问题绕晕了,各位仁兄解答一下吧: 设在但处理机系统中有n(n>2)个进程: (1)是否会出现等待队列为空的情况?为什么? (2)是否会出现等待队列为空且无进程运行的情况?为什么? (3)是否会出现就绪队列为空的情况?为什么? (4) ...… 查看全部问答> |

|

winCE5.0下串口程序无法接收数据!,请高手帮忙!! SOS... 下面是我在VS2005下用C#编写的,用在winCE5.0下的一个串口程序,在编译时出现了以下错误: ——“System.Windows.Form.Form”并不包含“CheckForIllegalCrossThreadCalls”的定义——如果 ...… 查看全部问答> |

|

硬件环境:硬件多普达智能手机带蓝牙. 软件环境:Smartphone. 程序主干: 1.g_hComDevice= RegisterDevice (L\"COM\", ComIndex, L\"btd.dll\", (DWORD)&pp); //创建虚拟串口,本地为服务器端 2.g_hComFile = CreateFile (szComPort, ...… 查看全部问答> |

|

UltraEdit的SystemVerilog关键词设置共享 SystemVerilog部分在文件末尾(/L15 打头),每个人的惯用语言不一样,如果你只需要增加SystemVerilog部分而保留其它设置,则把这最后一部分拷下贴到你的 WORDFILE.TXT中就可(别忘了把该文件设为WORDLIST文件:菜单-> 高级->配置->语法高 ...… 查看全部问答> |

|

在同一块电路板上,由于信号线的走线过长而产生的高频毛刺我们可以通过在接近输入端串联一个100欧左右的电阻来滤除。但是对于板外信号,或者板内其他干扰造成较大的抖动时只好采用积分电路来滤波,即串一个电阻还要并一个电容接地。 同样在VHDL ...… 查看全部问答> |