ARM64硬件中断处理机制深度解析

2025-12-03 来源:elecfans

一、先搞懂:什么是硬件中断?

你正在用刷视频,突然收到微信消息——这就是生活中的“中断”。对64(手机、服务器、设备的核心)来说,硬件中断是外设(如键盘、网卡、)向发送的“紧急请求”:比如网卡收到数据要处理、到点要触发任务、按键被按下要响应,这些都需要CPU暂停当前工作,优先处理紧急事务。

没有中断机制的话,CPU只能“轮询”外设(挨个问“有没有事?”),既浪费资源又反应迟钝。而中断就像“快递敲门”,CPU不用一直等,收到再切换任务,效率直接拉满。

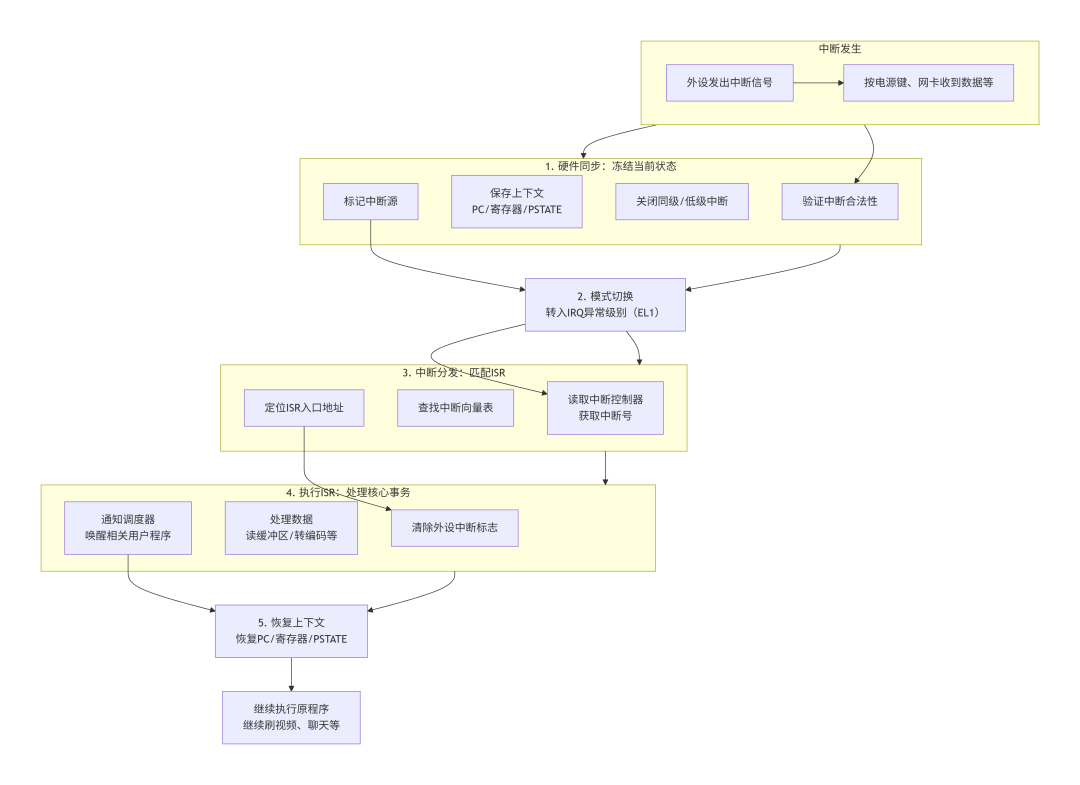

二、中断触发后,ARM64的“五步应急流程”

当硬件外设发出中断信号(比如你按了手机电源键),ARM64处理器会立刻启动一套标准化处理流程,全程由硬件+固件+协同完成,快到微秒级:

1.硬件同步:冻结当前状态,锁定中断源

•处理器首先检测中断信号的“合法性”(避免虚假中断),确认是来自有效外设的请求;

•立刻保存当前执行上下文:把PC(程序计数器,记录下一条要执行的指令地址)、值、程序状态字(PSTATE,记录CPU当前工作模式)等关键信息,压入对应模式的栈(如IRQ栈);

•自动关闭同级或低级中断(防止中断嵌套混乱),同时标记中断源(比如“键中断”“网卡中断”),让后续流程知道该处理什么。

2.模式切换:从“用户态/内核态”转入“中断模式”

ARM64有多种工作模式(EL0用户态、EL1内核态、EL2虚拟化态等),中断发生时,CPU会强制切换到IRQ异常级别(EL1)——这是专门处理硬件中断的“特权模式”,只有内核才能访问。

•举个例子:你正在用APP(EL0用户态)聊天,此时网卡收到数据触发中断,CPU会暂停APP执行,切换到EL1内核态,准备处理数据。

3.中断分发:找到“负责处理的内核程序”

ARM64的中断(如GICv3/GICv4)会把中断信号“翻译”成内核能识别的编号(中断号),然后通过以下步骤分发:

1.内核读取中断控制器的寄存器,获取中断号;

2.查找“中断向量表”(内核中预设的“中断处理清单”),根据中断号找到对应的“中断服务程序(ISR)”——比如网卡中断对应“网卡数据接收ISR”,键盘中断对应“键盘输入处理ISR”;

3.跳转到ISR的入口地址,开始执行具体处理逻辑。

4.执行中断服务程序(ISR):处理核心事务

ISR是内核中专门处理某类中断的小程序,逻辑简洁(避免占用CPU太久),核心工作包括:

•硬件层面:告知外设“我已经收到中断,你可以停止发送请求了”(清除中断标志);

•数据层面:处理外设传递的数据(如网卡ISR读取网卡缓冲区的数据,存入内存;键盘ISR读取按键编码,转换成字符);

•任务调度:如果中断处理后需要唤醒用户态程序(如收到微信消息后唤醒聊天APP),ISR会通知内核调度器,后续恢复APP执行。

5.恢复上下文:回到中断前的工作状态

ISR执行完毕后,CPU会做最后一步:恢复中断发生前的上下文:

•从栈中取出之前保存的PC、寄存器值、PSTATE;

•切换回原来的工作模式(如EL0用户态);

•跳回中断前的指令地址,继续执行原来的程序(比如继续聊天、刷视频)。

整个过程一气呵成,用户完全感知不到CPU的“切换操作”——这就是中断机制的神奇之处:既保证了紧急事务的优先处理,又不影响正常工作。

三、ARM64中断处理的“关键优化”:为什么这么快?

ARM64作为高性能架构,在中断处理上有两个核心优化,让响应速度远超传统架构:

1.向量表基址可配置:中断向量表可以放在高速缓存(Cache)中,内核查找ISR时无需访问内存,速度更快;

2.中断嵌套支持:通过GIC控制器和内核配置,支持“高优先级中断打断低优先级中断”——比如正在处理键盘中断时,来了更紧急的定时器中断(如实时任务触发),CPU会暂停键盘ISR,先处理定时器中断;

3.虚拟化友好:GICv4控制器支持中断直接投递到虚拟机(VM),无需经过物理机内核中转,提升虚拟化场景(如云服务器)的中断效率。

四、总结:中断是ARM64的“高效协作核心”

硬件中断就像ARM64处理器的“应急响应系统”,核心价值是实现CPU与外设的异步协作——CPU不用盯着外设,外设有事直接“喊” CPU,既提升了CPU利用率,又保证了设备的实时响应。

从手机的触控响应、的网卡数据接收,到服务器的多任务并发,背后都离不开ARM64的中断处理机制。正是这套“快速响应、精准分发、高效恢复”的流程,让我们的设备能流畅处理各种复杂任务。

进入嵌入式查看更多内容>>

- 嵌入式的风向变了:2026纽伦堡嵌入式展透露这些趋势

- 高通确认不在GDC 2026发布新款骁龙G系列掌机处理器SoC

- 行业评论 从工具到平台:如何化解跨架构时代的工程开发和管理难题

- 面向嵌入式部署的神经网络优化:模型压缩深度解析

- 摩尔线程MTT S5000全面适配Qwen3.5三款新模型

- Mujoco中添加Apriltag标签并实现相机识别教程

- 英飞凌与宝马集团携手合作,基于Neue Klasse架构塑造软件定义汽车的未来

- 物理AI仿真新突破:摩尔线程与五一视界共建全栈国产化生态

- 阿里达摩院发布玄铁C950,打破全球RISC-V CPU性能纪录

- 爆火的OpenClaw! 告别云端,米尔RK3576开发板本地部署

- 边缘计算主机盒选购指南:五大核心指标解析

- Arm AGI CPU 更多细节:台积电 3nm 制程、Neoverse V3 微架构

- Arm AGI CPU 重磅发布:构筑代理式 AI 云时代的芯片基石

- Arm 拓展其计算平台矩阵,首次跨足芯片产品

- 阿里达摩院发布RISC-V CPU玄铁C950,首次原生支持千亿参数大模型

- 边缘 AI 加速的 Arm® Cortex® ‑M0+ MCU 如何为电子产品注入更强智能

- 阿里达摩院发布玄铁C950,打破全球RISC-V CPU性能纪录

- VPU中的“六边形战士”:安谋科技Arm China发布“玲珑”V560/V760 VPU IP

- 利用锚定可信平台模块(TPM)的FPGA构建人形机器人安全