什么是PCI Express 高速串行互联接口标准?

2025-08-14 来源:21ic

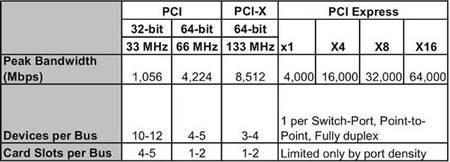

PCI Express|0'>PCI Express是从PCI发展而来的一种系统互联接口标准。PCI和PCI-X都是基于32位以及64位的并行总线,而PCI Express则使用高速串行总线。PCI Express后向兼容于PCI,能够灵活地提供大峰值带宽。表1对比了三种PCI标准的特性。

表1 PCI标准对比

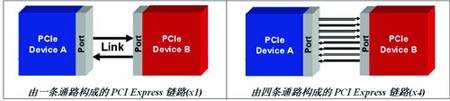

一对同时工作的发送和接收通道被称为一个通路。发送和接收通道使用低电压差分信号(LVDS)标准传输数据。数据时钟嵌入在每个通道中,以实现非常高的数据速率。

图1 PCI Express链路

一条PCI Express链路由多条通路组成,在链路中增加更多的通路可提高PCI Express链路的带宽。规范支持的链路通路带宽有x1、x4、x8和x16四种。

PCI Express的高级特性包括:

主动功耗管理:在PCI Express中,不管总线上是否有信号传送,总线接口总是一直在工作。空闲状态下,总线上没有任何操作时,这样会导致很高的功耗。为降低功耗,PCI Express提供了主动功耗管理机制,以便降低总线空闲时的功耗。

实时数据流量:PCI Express保证数据包在虚拟通道的给定时间内到达其目的地,实现了不同等级的服务质量(QoS)。

热插拔:PCI Express支持系统工作时的热插拔,缩短了系统更新和调试阶段的停机时间。

误码探测和纠正:由于数据链路层的循环冗余码校验(CRC)功能,PCI Express能够更好地检查数据完整性,进行误码处理,提高总线操作的可靠性,增强数据恢复的能力。

实现PCI Express接口的难点

采用定制逻辑在专用产品中实现PCI Express接口有很多难点:

自适应硬件:设计专用产品所选用的硬件平台必须能够满足PCI Express协议的电气规范和性能要求。在存储器、服务器和背板等典型PCI Express终端应用中,基于PC的网络在带宽需求和数据速率上发展很快。这类产品还需要灵活地适应那些可能替代现有标准的新标准。

系统性能:由于PCI Express链路的预期数据速率在Gbps范围内,因此,时序裕量非常紧张。实现任何PCI Express接口都必须满足系统严格的性能要求。

可靠性:要实现这一协议必须保证产品在可能经受的工作电压和温度(PVT)变化范围内有可靠的性能表现。

通用性:PCI Express接口经常用于连接不同的半导体器件。因此,该协议的产品必须与市场上其他PCI Express器件兼容。

使用方便:对于系统设计人员而言,PCI Express应该实现起来比较简单(或者换句话说,打开包装就能用)。这一般是指能够提供参考设计、界面友好的软件工具、验证设计的原型开发平台,以及完整的文档等。

FPGA中的PCI Express接口

FPGA通常用于桥接使用不同协议的器件。而且,由于逻辑门容量的增加,系统级特性的丰富,以及系统吞吐量的提高,FPGA还被逐步承担系统核心功能。

在最近几年中,FPGA供应商开始采用吉比特收发器模块等硬件IP来实现高数据速率的高速串行I/O接口。例如,Altera公司的Stratix II GX FPGA每通道数据速率高达6.375 Gbps。采用吉比特收发器模块,现在可以在一片FPGA中实现高速串行协议,包括千兆以太网、串行Rapid IO、PCI Express、XAUI和HD-SDI等。

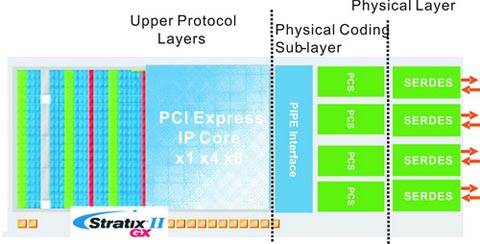

吉比特收发器模块一般包括物理层和物理编码子层(PCS),如图2所示。上层协议以硬件描述语言(HDL)编写的IP在FPGA架构中实现。

图2 PCI Express高速串行I/O

FPGA的PCI Express接口有明显的优势:

灵活性:由于FPGA架构在本质上具有可编程性,因此,采用FPGA的任何产品在通路数量、特性、实现定制硬件的可能性,以及与其他半导体器件的连接都有很大的灵活性。

容易更新:采用FPGA的产品能够适应协议和功能需求的变化。因此,这类产品能够避免过时,容易进行更新。

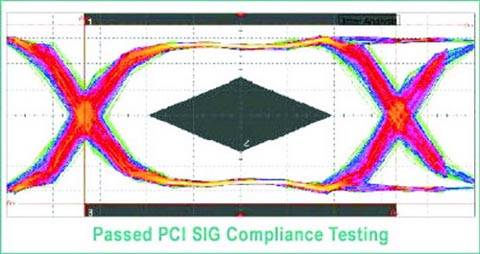

性能成熟:FPGA中的吉比特收发器模块能够保证具有时序裕量。图3中的PCI Express眼图经过验证,符合PCI-SIG标准。这意味着,用户甚至在启动设计之前,就可以确信产品的兼容性。

图3 Stratix II GX 中的PCI Express接口符合PCI-SIG

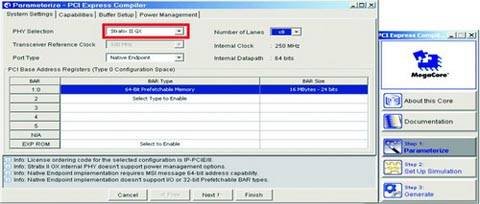

使用方便:FPGA供应商还提供开发板、参考设计和设计指南,降低了实现PCI Express接口的难度。例如,Altera提供界面友好的PCI编译器工具,很容易在Stratix II GX FPGA中对多通路PCI Express接口进行定制、构建和测试(图4)。

图4 使用方便的PCI编译器软件工具

通用性:Stratix II GX FPGA在与其他PCI Express兼容器件在通用性上成功地通过了测试,例如Freescale公司的PowerQUICC III处理器。

FPGA中集成了吉比特收发器之后,以前采用分立收发器芯片的高速系统设计人员,现在可以充分利用FPGA的灵活性以及产品及时面市的优势,将精力集中在创造更高效能和降低风险上,同时他们还能够及时应对市场上的各种需求变化。

上一篇:什么是LCOS?

下一篇:基于智能手机创新交互界面的设计

- 常见测试测量接口的比较:PXI、PXIe、PCI、VXI、GPIB、USB

- Proximus Global旗下公司Telesign与PCI Pal合作 助力企业提前发现支付欺诈行为

- 什么是PCI Express 标准(上)

- 什么是PCI Express 标准(中)

- 是德科技助力 AMD 展示高达 64 GT/s 的电气 PCI Express® 合规性

- PCI Express Gen5:自动化多通道测试

- PCI Express发射器一致性/调试解决方案

- 博通重磅产品发布,引领PCI-e交换机和重定时器市场

- 基于C8051F021型单片机与PCI接口实现数据采集卡的设计

- 康佳特推出业界领先COM Express Compact模块,搭载AMD 锐龙™ AI嵌入式P100系列处理器

- 嵌入式的风向变了:2026纽伦堡嵌入式展透露这些趋势

- 高通确认不在GDC 2026发布新款骁龙G系列掌机处理器SoC

- 行业评论 从工具到平台:如何化解跨架构时代的工程开发和管理难题

- 阿里达摩院发布玄铁C950,打破全球RISC-V CPU性能纪录

- 面向嵌入式部署的神经网络优化:模型压缩深度解析

- Mujoco中添加Apriltag标签并实现相机识别教程

- 摩尔线程MTT S5000全面适配Qwen3.5三款新模型

- 英飞凌与宝马集团携手合作,基于Neue Klasse架构塑造软件定义汽车的未来

- 物理AI仿真新突破:摩尔线程与五一视界共建全栈国产化生态

- 爆火的OpenClaw! 告别云端,米尔RK3576开发板本地部署

- Altera 与 Arm 深化合作,共筑 AI 数据中心高效可编程新方案

- 莱迪思加入英伟达 Halos生态系统,通过Holoscan传感器桥接技术提升物理人工智能安全性

- 芯科科技闪耀2026嵌入式世界展 以Connected Intelligence赋能,构建边缘智能网联新生态

- 边缘计算主机盒选购指南:五大核心指标解析

- Arm AGI CPU 更多细节:台积电 3nm 制程、Neoverse V3 微架构

- Arm AGI CPU 重磅发布:构筑代理式 AI 云时代的芯片基石

- Arm 拓展其计算平台矩阵,首次跨足芯片产品

- 阿里达摩院发布RISC-V CPU玄铁C950,首次原生支持千亿参数大模型

- 边缘 AI 加速的 Arm® Cortex® ‑M0+ MCU 如何为电子产品注入更强智能