如何选择合适的工业以太网标准:EtherCAT

2025-09-17 来源:elecfans

在这一部分中,我将详细介绍EtherCAT、它的终端应用,以及它的工作方式。

德国倍福自动化公司 (Beckoff Automation) 发明了EtherCAT。自从2003年以来,它一直处于EtherCAT技术组 (ETG) 框架之下,而EtherCAT技术组是一个由大约2600家成员公司组成的工业现场总线组织。

EtherCAT常见于工厂自动化、半导体工具、包装机器人技术以及其它应用领域。我最喜欢的一个非工业应用示例就是迪斯尼内的水舞水幕秀,其中由EtherCAT来控制灯光显示。

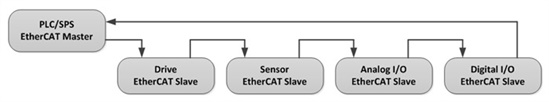

在技术层面,EtherCAT是如图1中显示的主从网络架构。EtherCAT从器件具有2个以太网连接器,以支持一个简单的线路拓扑。为了达到冗余的目的,也可以支持环形拓扑,在这个情况下,EtherCAT主器件必须要有2个以太网端口。一个EtherCAT网络能够支持多达65535个从器件。

图1:具有EtherCAT数据帧流程的EtherCAT主从示例网络

只有EtherCAT主器件生成一个EtherCAT数据帧;所有从器件接收和处理这个数据帧。最后一个从器件回送这个EtherCAT数据帧,而这个数据帧在经历所有从器件(无需进一步处理)后,返回到主器件。这个EtherCAT数据帧已经为每个从器件的数据处理预留了空间,而所有的从器件都不会更改数据帧本身的长度。这有点儿像为乘客准备了多个车厢和座位的火车一样,每个从器件都有一个指定的车厢或指定的座位。EtherCAT允许到“座位”层的寻址—而数据处理是在数据位上进行的。

一个EtherCAT主器件只需要一个标准以太网MAC外设,这是因为主器件在实时处理EtherCAT数据帧方面没有特定的需要。主器件只需要用准确的时基来触发启动EtherCAT数据帧。

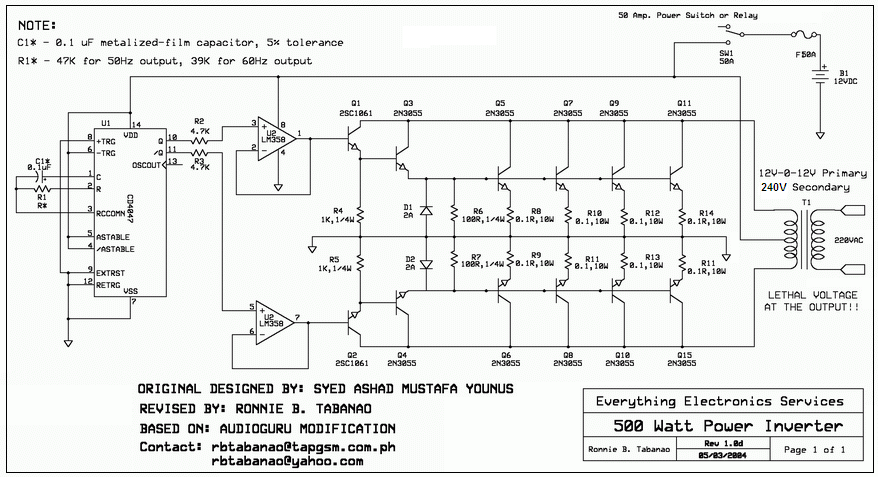

一个EtherCAT从器件需要特定的以太网硬件 (EtherCAT MAC) 支持—通常的实现方式是图2中所示的专门用途集成电路 (ASIC) 或现场可编程门阵列 (FPGA) –这是因为它需要处理在运行过程中进入的EtherCAT数据帧。这意味着EtherCAT MAC在进行数据帧接收的同时,要处理EtherCAT数据帧。典型的EtherCAT器件在已接收和已发送数据帧之间具有1µs的端口到端口延迟。

图2:具有一个ASIC/FPGA和外部处理器的EtherCAT从器件

EtherCAT标准在EtherCAT网络中不支持其它类型的以太网数据帧。这主要是为了保持实时以太网通道的畅通,用于EtherCAT数据帧的处理。在EtherCAT网络中有非EtherCAT数据帧(与EtherCAT不匹配的以太网类型)的情况下,EtherCAT从器件将通过使数据帧校验和 (CRC) 无效来销毁这个数据帧。这使得非EtherCAT数据帧在标准以太网器件中无法使用,而它们将最终停止“污染”EtherCAT网络。

通过将以太网数据帧封装在一个EtherCAT数据帧内,可以在EtherCAT网络中传送标准以太网数据帧(传输控制协议/互联网协议 (TCP/IP),用户数据报协议 (UDP))。这通过位于EtherCAT主机处理器协议栈顶端的不同EtherCAT系统配置完成。其中的一个示例系统配置就是用EtherCAT实现以太网。

EtherCAT器件的其它特性和功能包括:

分布时钟—从器件和主器件上的高精度时间同步方法。

支持环回的快速链路断开检测(需要以太网物理层 (PHY) 收发器支持)--当以太网PHY检测到一个链路断开时,它通知EtherCAT硬件。在10µs内,EtherCAT硬件将环回EtherCAT数据帧。请查看TI的TLK1xx以太网PHY收发器系列,这个系列的器件支持快速链路断开特性。

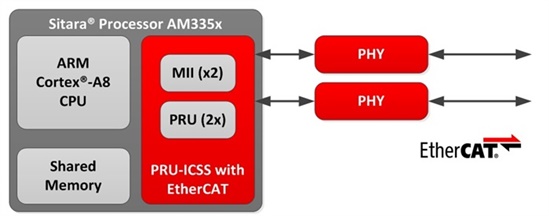

在EtherCAT中使用ASIC或FPGA会增加成本和电路板面积。一个替代的解决方案就是使用许多TI Sitara处理器中的PRU-ICSS外设。例如,TI提供针对AM335x处理器的PRU-ICSS固件,从而使EtherCAT从器件无需使用一个外部FPGA(图3)。你可以用TMDSICE3359评估板来评估TI的EtherCAT从器件解决方案。

图3:集成了TI Sitara处理器的EtherCAT从器件

- 嵌入式的风向变了:2026纽伦堡嵌入式展透露这些趋势

- 高通确认不在GDC 2026发布新款骁龙G系列掌机处理器SoC

- 行业评论 从工具到平台:如何化解跨架构时代的工程开发和管理难题

- 面向嵌入式部署的神经网络优化:模型压缩深度解析

- 阿里达摩院发布玄铁C950,打破全球RISC-V CPU性能纪录

- Mujoco中添加Apriltag标签并实现相机识别教程

- 摩尔线程MTT S5000全面适配Qwen3.5三款新模型

- 英飞凌与宝马集团携手合作,基于Neue Klasse架构塑造软件定义汽车的未来

- 物理AI仿真新突破:摩尔线程与五一视界共建全栈国产化生态

- 爆火的OpenClaw! 告别云端,米尔RK3576开发板本地部署

- 莱迪思加入英伟达 Halos生态系统,通过Holoscan传感器桥接技术提升物理人工智能安全性

- 芯科科技闪耀2026嵌入式世界展 以Connected Intelligence赋能,构建边缘智能网联新生态

- 边缘计算主机盒选购指南:五大核心指标解析

- Arm AGI CPU 更多细节:台积电 3nm 制程、Neoverse V3 微架构

- Arm AGI CPU 重磅发布:构筑代理式 AI 云时代的芯片基石

- Arm 拓展其计算平台矩阵,首次跨足芯片产品

- 阿里达摩院发布RISC-V CPU玄铁C950,首次原生支持千亿参数大模型

- 边缘 AI 加速的 Arm® Cortex® ‑M0+ MCU 如何为电子产品注入更强智能

- 阿里达摩院发布玄铁C950,打破全球RISC-V CPU性能纪录