伴芯科技正式发布AI智能体 以大模型重构芯片设计效率

2025-12-03 来源:EEWORLD

电子工程世界,冀凯

在ICCAD-Expo 2025现场,伴芯科技CEO朱允山博士正式对外发布面向芯片设计领域的AI智能体——DVcrew与PDcrew。这两款产品深度契合伴芯科技的核心使命:以AI智能体(AI Agents)重构电子设计自动化(EDA),最终实现芯片自主设计闭环(Autonomous Chip Design)的愿景,也展现了Agentic EDA这一新范式的应用前景。

作为一家聚焦大模型与芯片设计融合应用的创新企业,伴芯科技的此次发布标志着国内EDA行业在AI赋能领域迈出了实质性步伐。

伴芯科技CEO朱允山博士

详解DVcrew与PDcrew

DVcrew:专注于设计验证的核心利器。

设计验证是芯片设计流程中公认的核心难题,功能失效是导致流片失败的首要原因。功能验证环节不仅占据最长的研发周期,验证团队规模通常也是RTL设计团队的2至5倍,使其成为芯片设计中最严峻的挑战。SoC芯片设计集成了多个处理器及数百个组件,验证工作需确保每个组件的RTL代码及其间所有交互的正确性,其复杂性不言而喻。设计验证工程师表示,在芯片中发现所有bug需要99%的努力和1%的运气,而DVcrew的目标,正是通过AI智能体将这1%的运气成分降至最低。在芯片中发现一个bug,需要找到一个引发bug的测试向量序列,并且可观察到checker或者断言的触发。DVcrew像一个高度成熟的设计验证团队合作伙伴,它融合了AI智能体、RTL分析、规格说明分析、仿真轨迹与形式化验证等多种先进技术,生成适用于各种验证环境的断言,并高效发现深层漏洞,在设计验证中使用DVcrew,客户有望在提升芯片质量的同时,显著降低整体设计验证成本。

PDcrew:破解物理设计的不确定性。

一旦前端设计人员完成RTL freeze,芯片流程的挑战就转移到物理设计,就是将网表转换为代工厂能接受的GDS版图。这一转换是芯片设计流程中最不确定的环节,因为它深受RTL网表和芯片物理设计约束的影响。伴芯科技历经数年时间研发新一代布局布线引擎,适用于智能体框架,旨在流程中减少人工参与,提供从网表到GDS的一站式解决方案。PDcrew也为工程变更(ECO)流程提供高效解决方案,设计师可以在尽量减少设计或掩膜更改的情况下完成变更需求。网表到GDS转换中的自主流程智能体能够每周7天、每天24小时运行,持续优化芯片的性能、功耗和面积(PPA)。

AI智能体与知识库的双轮驱动

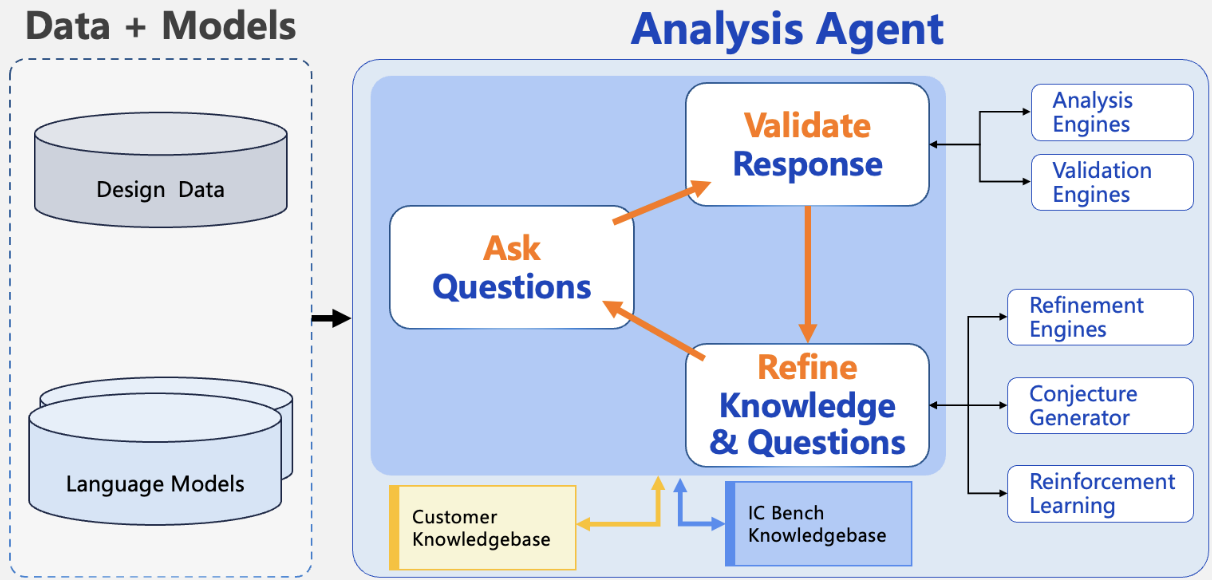

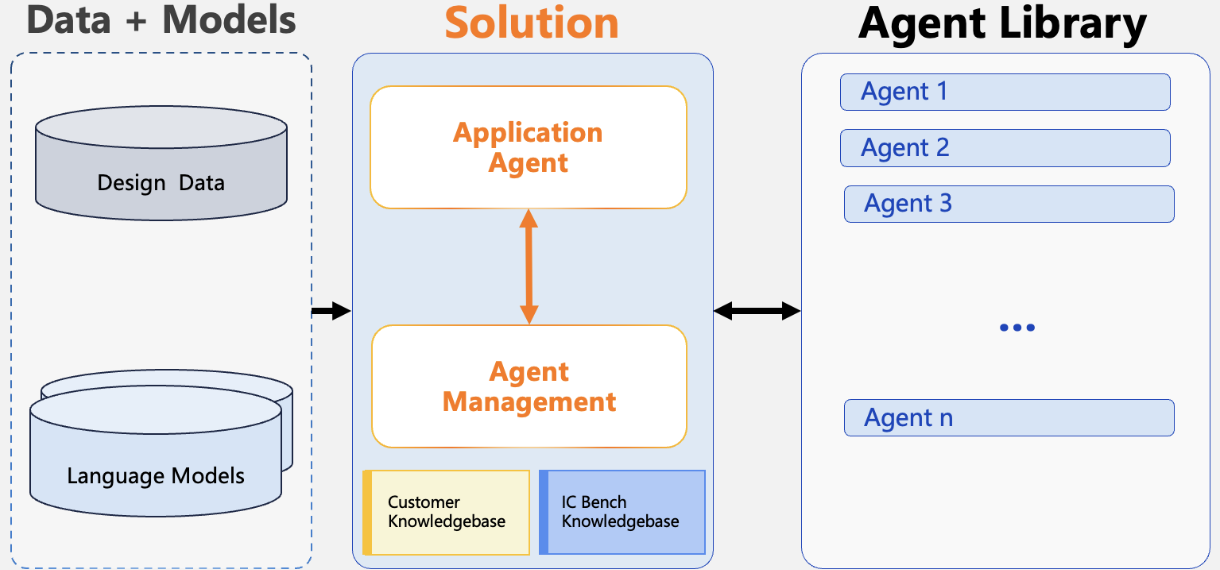

AI智能体是驱动DVcrew与PDcrew实现EDA架构突破的核心。伴芯科技对重构EDA的关键贡献在于其独有的知识库体系。

公司为产品配备了一个经过芯片设计与EDA专家经验锤炼的指导性知识库,用于为大型语言模型(LLM)提供精准的任务指引,确保其在特定任务中进行分析的准确性。同时,产品还提供了客户专属知识库,允许客户将私有的技术经验及设计规范注入EDA智能体流程,形成独特的技术壁垒。

在这种“分析-验证-优化”的迭代模式下,AI智能体能够有效避免幻觉,直至精准完成任务。DVcrew与PDcrew内部集成了多个AI智能体,并有效协同自主解决芯片设计的各项挑战。

AI智能体如何赋能EDA

“我们是EDA公司,又不止于EDA公司。”朱博士明确了伴芯科技的差异化定位。自2020年成立以来,伴芯科技打破了传统EDA企业聚焦底层数据结构优化的路径依赖,将核心能力集中于大模型在芯片设计中的应用落地。这一创新理念已获得资本市场的高度认可,目前已完成多轮融资,投资方包括红杉中国、联想创投、顺为资本、弘晖基金等众多知名机构。

在商业化进展方面,伴芯科技已取得实质性成果。据朱博士透露,公司在未正式发布前已与全球前20的顶尖芯片设计公司及国内外多家头部企业建立深度合作。

谈及技术研发路径,朱博士强调了“整合创新”的核心逻辑。伴芯科技并非从零构建大模型,而是通过对顶尖开源大模型进行微调与强化学习优化,结合自主开发的EDA软件接口,实现大模型与设计工具的深度融合。

朱博士还强调了伴芯科技的三大核心竞争力:大模型优化能力、EDA工具接口整合能力以及对芯片设计流程的深入理解能力。这三大能力共同构成了其发展实用EDA智能体、推动Agentic EDA落地的坚实基础。

而如今,面对三大国际EDA巨头基于AI智能体的竞争,朱博士展现出充分信心。其表示,在Agentic EDA这一新兴赛道上,行业所有竞争者都处于同一起跑线。

另外,伴芯科技“船小好掉头”,核心团队涵盖前端设计、后端设计及AI应用领域专家,能够打破传统大企业的部门壁垒,实现全流程协同优化,有效解决大模型应用中的“幻觉问题”,保障芯片设计的准确性。“传统巨头的既有模式难以快速适应颠覆性创新,这为初创企业创造了机遇。”

同样,在大家都关注的数据安全上,伴芯科技坚决采用“本地化部署”策略,将大模型与软件部署于客户自有网络环境,打消了企业对核心设计数据外泄的顾虑。

来自客户的声音

目前伴芯科技的产品已陆续交由客户处评估,也有多家客户在试用过之后给与了高度评价,以下节选了部分用户的发言。

遇贤微电子首席技术官表示:“Al-native EDA是芯片行业下一个重要里程碑。DVcrew以AI重新定义验证流程,将设计断言编写从手工劳动升级为智能生成。其卓越的corner case缺陷挖掘能力,直面芯片验证的核心挑战,为大算力芯片验证提供了全新维度,是AI在EDA领域落地的一项标志性成果。”

SemiDrive Verification Team Lead表示:“在评估IC Bench DVcrew的头几天,他们就发现了我们设计中的一个缺陷,这让我们惊喜不已。我们非常幸运,伴芯能够以验证团队极低的人力投入,识别出设计中难以预见的错误。DVcrew无疑是设计验证领域的一项独具匠心的创新!”

奉加科技总经理表示:“验证低功耗蓝牙SoC涉及复杂的状态机和射频接口时序。DVcrew提供了一个端到端的自动化验证流程来应对这些挑战。它显著加快了我们的验证周期,并增强了我们对实现全面设计空间覆盖的信心。”

芯翼科技研发副总表示:“DVcrew的本地化部署模式让我们能够立即开始使用,且无需担心安全问题。它能快速处理我们的代码库,并以极快的速度提供高质量的验证结果。

“发挥中国开源大模型优势,构建产业协同生态,是解决EDA卡脖子问题的新路径。”朱允山博士对产业界发出呼吁,希望联合芯片设计、EDA及大模型领域的合作伙伴,共同探索Agentic EDA的技术创新方向。

- 伴芯科技重磅发布DVcrew与PDcrew两大创新产品,以AI智能体重构EDA

- 伴芯科技重磅亮相!AI智能体重构EDA,迈向芯片自主设计闭环

- 新势力伴芯科技加速成长

- 继红杉中国之后,伴芯科技获联想创投新一轮战略融资

- 国内首款Agentic AI自研EDA平台,合见工软发布智能体UDA 2.0重塑芯片设计范式

- 从概念到芯片:新思科技EDA+车规IP赋能芯粒架构汽车SoC设计

- 硅芯科技赵毅:共建“EDA+”体系,迎接产业新范式

- 锐成芯微杨毅:以全栈 IP 布局赋能 AIoT 3.0 演进

- 合见工软徐昀:国产EDA赋能,筑牢智算产业自主根基

- 启芯领航廖鼎鑫: 国产 EDA 替代不能依赖情怀,更需要产品实力