RF技术用于TSMC 65纳米工艺节点

2008-04-16 来源:电子工程世界

Cadence QRC Extraction和Virtuoso Passive Component Designer目前已经被包含在TSMC工艺设计工具包中以解决RF关键问题。

这次新认证的技术提供了经过测试的、可靠的电感、衬底提取和无源元件设计。QRC Extraction能够进行寄生电感和底层提取,而新发布的Virtuoso Passive Component Designer技术可以进行电感综合、分析和建模。在6月份,Cadence和TSMC推出了一种TSMC CompatibleSM 65纳米RF PDK,使用最新的Cadence Virtuoso定制设计平台,并附带可下载的RF、模拟和混合信号(RF和AMS)设计流程示范包提供给无线设计师。

该Cadence技术被认证为新TSMC电磁(EM)工具认证计划(TSMC Electromagnetic (EM) Tool Qualification Program)的一部分,面向TSMC 90和65纳米工艺技术。该计划确保对高速数字时钟电路和高频混合信号RF设计流程有更高的电磁精确度。

基带电路、微处理器和内存进入到最高级的CMOS工艺节点。为启用系统级芯片上的无线系统,RF收发器和频率合成器必须贯彻使用相同的工艺。使用QRC Extraction对衬底的精确建模签收和对互联线路的RLCK提取,RF设计师就可以提高一次性芯片成功的可能性,并降低总设计成本。使用噪声周线图的假设分析法让设计师能够在噪声较多的数字电路周围迅速实验RF模块的各种不同放置方案。

TSMC 65纳米PDK包含由Virtuoso Passive Component Desgner提供的可调整的感应器和变压器模型。模型精确性已经在感应系数、品质因数和自谐振频率等指标方面被验证与实测结果相差只有百分之几的量级。

设计师不再被局限于一定数量的PDK感应器范围之内。从感应系数和品质因数等设计指标开始,RF设计师可以在Passive Component Designer中创造他们自己的感应器和变压器,使用TSMC PDK提供的可调整的参数化的模块。这种新技术能够读取TSMC 65纳米规则档案,并合成没有DRC和LVS错误的元件,随时可用于QRC Extraction分析。Virtuoso Passive Component Designer支持65纳米效应如衬底偏压、侵蚀、金属填充和切削。

- 支持GLOBALFOUNDRIES 65纳米工艺的参考流程

- 65纳米工艺技术的DesignWareUSB 2.0 nanoPHY

- 支持SMIC 65纳米工艺的低功耗参考流程

- 英特尔大连厂采用65纳米工艺获美国政府批准

- 中芯国际发布65纳米低漏电工艺的IP产品

- Impinj欲推65纳米NVM,将内存整合到CMOS工艺中

- 安华高在65纳米CMOS工艺上取得17Gbps SerDes输出

- 中芯国际65纳米工艺年底投产 看好中国市场

- Avnet加速毫米波设计,联合赛灵思推出RFSoC开发工具包

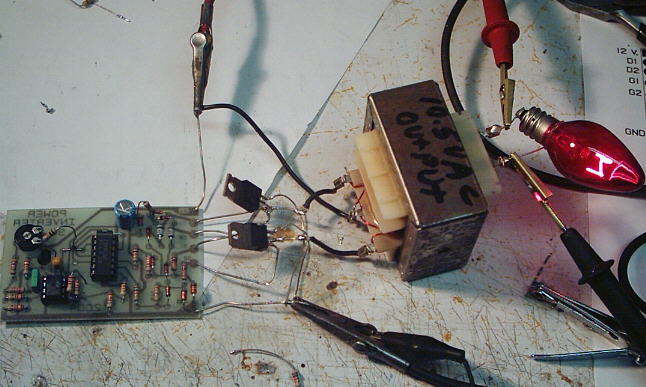

- 助力逆变器设计 Microchip推出业界唯一低电感碳化硅(SiC)功率模块和可编程栅极驱动器工具包

- AMD二代 Versal™ SoC出道,单芯片扛下了AI三个阶段的全加速

- AI持续发热,Arm新一代Neoverse CSS V3和CSS N3为客户释放最优性能

- 米尔入门级i.MX6UL开发板的神经网络框架ncnn移植与测试

- 博格华纳向Wolfspeed投资5亿美元,保障高达6.5亿美元碳化硅器件年度产能供应

- 艾迈斯欧司朗推出新型高灵敏度三通道CMOS传感器,有效降低UV-A/B/C辐射监测成本

- 我国科学家实现658公里量子密钥分发和光纤振动传感

- 以铁代铂金,科学家发明低成本氢燃料电池

- 特斯拉汽车能用太阳能开1.5万公里?这种材料或许可以

- 美国可穿戴技术公司Eckto VR推出VR运动鞋“Ekto One”