历史上的今天

今天是:2024年10月15日(星期二)

2021年10月15日 | STM32系统时钟树分析

2021-10-15 来源:eefocus

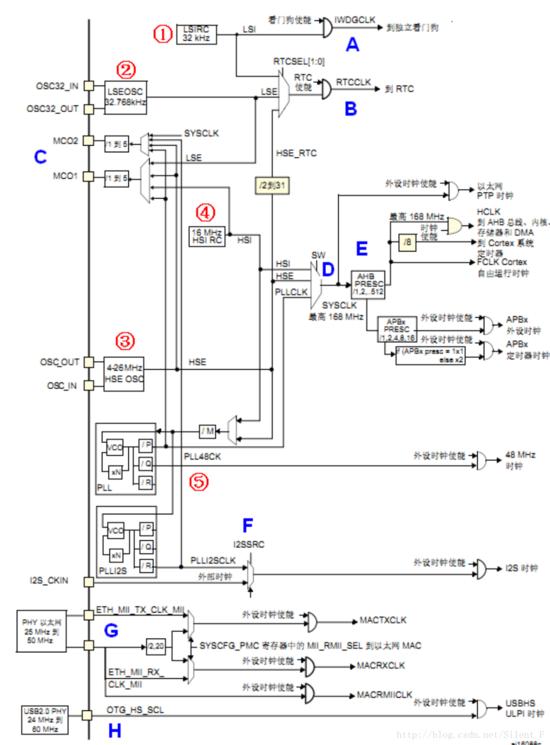

下面是一个STM32芯片的时钟树图

1、LSI是低速内部时钟,RC振荡器,频率为32kHz左右。供独立看门狗和自动唤醒单元使用。

2、LSE是低速外部时钟,接频率为32.768kHz的石英晶体。这个主要是RTC的时钟源。

3、HSE是高速外部时钟,课接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~26MHz。我们开发板接的是8M的晶振。HSE也可以直接作为系统时钟或者PLL输入。

4、HSI是高速内部时钟,RC振荡器,频率为16MHz。可以直接作为系统时钟或者用作PLL输入。

5、PLL为锁相环倍频输出。STM32F4有两个PLL:

(1)主PLL由HSE或者HSI提供时钟信号,并具有两个不同的输出时钟。

第一个输出PLLP用于生成高速的系统时钟(最高168MHz)

第二个输出PLLQ用于生成USB OTG FS的时钟(48MHz),随机数发生器的时钟和SDIO时钟。

(2)专用PLL(PLLI2S)用于生成精确时钟,从而在I2S借口实现高品质音频性能。

大家在图中可以看到一些梯形,这些梯形为选择器。左边为选择器,右边为分频器

LSI,低速内部时钟

LSI低速内部时钟,频率为32kHz。RC振荡器产生,因为是RC振荡器产生,所以频率不是很稳定。主要对右边的独立看门狗做时钟。因为独立看门狗对时钟的精度要求不是很高,所以可以使用LSI。LSI比较简单,简单的理解就是一个电阻一个电容。

LSI还可以作为RTC模块的时钟来源。在RTC模块左边有一个选择器,那么它不仅可以选择LSI作为时钟来源,还可以选择LSE作为时钟来源。

LSE,低速外部时钟

LSE一般是由外接的一个精确的32.768k的晶振产生,比较稳定,一般情况下RTC选择LSE作为时钟源。RTC的时钟来源还可以来自HSE(图上有线连着,顺着线找)。

MCO1/MCO2

在LSE下面有MCO1和MCO2两个引脚,这两个引脚就是把芯片内部的时钟输出到引脚。MCO1对应的是PA8,MCO2对应的是PC9(笔者这里使用的STM32F407芯片),MCO1和MCO2都有一个选择器,可以选择四个时钟来源,选择好时钟来源后经过一个分频器,分频就是对时钟进行除法运算,然后再输出到对应的引脚。

HSE,高速外部时钟

HSE是由外接的晶振产生的,是4MHz~26MHz。HSE产生时钟后会先经过一个分频器,这个分频系数是2~31,分频后的时钟才可以作为RTC时钟的一个选择。

HSI,高速内部时钟

由RC振荡器产生,精度不高。首先,可以作为MCO1的一个时钟来源,其次可以作为系统时钟的一个来源。向下会将时钟信号送给一个选择器,这个选择器可以选择来自HSE和HSI的信号。左边一个“/M”的分频器,会把选择的时钟/M之后产生一个频率,产生一个频率后就到了PLL。

PLL,锁相环倍频输出

上面的叫主PLL,下面的叫专用PLL。主PLL产生两种时钟,一种作为系统时钟;一种叫作PLL48CK的时钟,用于USB OTG的时钟。专用PLL时钟主要是给I2S模块使用,因为I2S主要处理音频问题,对于频率的要求比较高,所以就有一个专用PLL。时钟信号从“/M”分频器出来后,进入“xN”的倍频器,然后在“/P”、“/Q”或者“/R”,“/P”出来后作为系统时钟;“/Q”出来后作为PLL48CK时钟;“/Q”出来后作为I2S时钟。从这里我们就能计算出从PLL出来的时钟频率,假设从选择器进去的时钟频率为f,PLL=(f/M)(N/P)或者PLL=(f/M)(N/Q)或者PLL=(f/M)*(N/R)。

图中A~G表示的地方:

A: 这里是看门狗时钟输入。从图中可以看出,看门狗时钟源之恩给你是低速的LSI时钟。

B: 这里是RTC时钟源,从图上可以看出,RTC的时钟源可以选择LSI,LSE,以及HSE分频后的时钟,HSE分频系数为2~31。

C: 这里是STM32F4输出时钟MCO1和MCO2。MCO1是芯片的。PA8引脚输出时钟。它有四个时钟来源分别为:HSI,LSE,HSE和PLL时钟。MCO2是向芯片的PC9输出时钟,它同样有四个时钟来源分别为:HSE,PLL,SYSCLK以及PLLI2S时钟MCO输出时钟频率最大不超过100MHz。

D: 这里我们值得是以太网PTP时钟,AHB时钟,APB2高速时钟,APB1低速时钟。这些时钟都是来源与SYSCLK系统时钟。其中以太网PTP时钟是使用系统时钟。最大时钟为168MHz,APB2高速时钟最大频率为84MHz,而APB1低速时钟最大频率为42MHz。

F: 这里是指I2S时钟源。从图可以看出,I2S的时钟源来源于PLLI2S或者映射到I2S_CKIN引脚的外部时钟。I2S出于音质的考虑,对时钟精度要求很高。

G: 这是STM32F4内部以太网MAC时钟的来源。对于MII接口来说,必须向外部PHY芯片提供25MHz的时钟,这个时钟,可以由PHY芯片外接晶振,或者使用STM32F4的MCO输出来提供。然后,PHY芯片再给STM32F4提供ETH_MII_TX_CLK和ETH_MII_RX_CLK时钟。对于RMII接口来说,外部必须提供50MHz的时钟驱动PHY和STM32F4的ETH_RMII_REF_CLK,这个50MHz时钟可以来自PHY、有源晶振或者STM32F4的MCO。我们的开发板使用的是RMII接口,使用PHY芯片提供50MHz时钟驱动STM32F4的ETH_RMII_REF_CLK.

H: 这里是指外部PHY提供的USB OTG HS (60MHz)时钟。

下一篇:STM32时钟树分析

史海拾趣

|

发帖发问一个bootloader问题并邀请学习6410,PXA3XX等高级货的同志了! 这几天看了6410的eboot,并对nk.bin以及nk.nb0文件重新了解了一下,发现了很多疑问。 主要是我以前一直用ADS bootloader,现在觉得两者有不可思议的差别。 一、ADS bootloader没有拷贝全局变量到RAM的行为,但是eboot.nb0有——但是这两个格式的 ...… 查看全部问答> |

|

如题。用的2450的板子,wince5.0的平台。现在用IIC1接我的IC芯片。现在拿到手的IIC驱动是IIC0的,即用的GPE14\\GPE15,我需要将其换成IIC1,即GPB7\\GPB8。我做了如下修改: 1、 WINCE500\\PLATFORM\\SMDK2450\\Src\\Drivers\\IIC\\i2c.c中 //#de ...… 查看全部问答> |

|

我用的优龙YL2410开发板,最近想自己制作一个cramfs跟文件系统,参考网上比较著名的一个文档《Linux系统移植》的根文件系统制作部分自己制作了一个cramfs的文件系统my_rootfs.cramfs,其中busybox使用的是1.1.3。把my_rootfs.cramfs烧写到板子后发 ...… 查看全部问答> |

|

wince5.0 S3c2440官方bsp,带camera驱动 wince5.0 S3c2440官方bsp,带camera驱动: http://www.itxxh.cn/book/2440/zaxsw1565.shtml WINCE5.0系统下,OV9650 CAMERA驱动程序: http://www.itxxh.cn/book/2440/zaxsw1568.shtml… 查看全部问答> |

|

Bit-banding 又称为:极细微的位处理操作, 精确的位操作,位别名区。 为了减少读-修改-写(RMW)操作的时间,ARM在Cortex-M3处理器中引入了bit-banding技术。在bit-banding使能的处理器中,存储器映射的特定区域(SRAM和外设区)能够使用地址别 ...… 查看全部问答> |