基于FPGA和Qt技术的音频广播系统

2025-08-25 来源:eepw

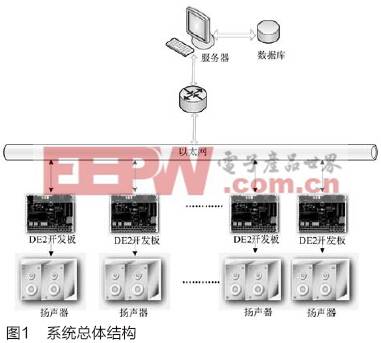

引言 随着数字和网络等技术的发展,广播技术已经呈现出越来越多元化的趋势,其最主要的趋势便是从模拟到数字的转化。从宏观来说,广播技术大体上可以分为三类:传统公共广播系统,采用的是定压式线路,传输损耗小,负载连接较为方便,但是传输的电压较高,需在扬声器端加接降压设备;数字可寻址音频广播系统,此类系统采用数字信号进行音频信号的传输,并具有可寻址特性,具有更远的传输距离和可靠性;流媒体(IP)智能广播系统,其特点是无需另行布线,结合网络的便利性,系统的扩展性进一步增强,将广播技术与其他技术进行充分融合,易于构建功能更加完善和易于管理的系统平台。 目前校园中使用的系统大都还停留在传统公共广播系统层次,由于线路老化等原因,如出现故障则不容易维修,而重新布线容易增加成本。基于此,本文提出一种使用FPGA和网络技术实现的音频广播方案,使用现有的网络线路进行数据的传输。因FPGA高度的可编程特性可以将控制电路做得更加集成,易于布设,同时增加了系统的可扩展性。 1 系统概述 本系统主要包括DE2播放终端(以下简称终端)以及服务器程序两部分。服务器程序负责制定并管理播放项列表以及与终端的交互,终端接收服务器发送的命令信息并驱动扩音设备播放所需音频。系统整体结构如图1所示。 由图1可以看到本系统支持多终端的管理,采用SD卡的方式进行音频广播是因为相较使用直接的数字编码在线路传输来说,SD卡的方式在需要播放音频时,只需由服务器发出相应的很短的命令报文至终端,这保证了各个扬声器播放在时间上的一致性。不会因为系统网络架构及解码速度不一致而产生播放进度不同步问题。因系统采用短命令报文形式且需进行广播传输,故系统使用的通信方式为UDP(User Datagram Protocol,用户数据报)的通信方式。 FPGA的可编程特性决定了其可参考资源很多,首要的参考资源为开发板自带光盘文件。通过查阅开发板光盘可发现与本项目相关的有两个资源:SD卡音乐播放系统,网络测试程序。SD卡音乐播放系统实现了本项目中所需要的SD卡音频播放功能。网络测试程序只是通过硬编码的形式将一个以太网帧通过DM9000A网卡发送出去,没有实现本系统所需的UDP协议及解析工作。依托于Altera提供的现有平台,可将系统工作简化为实现一个具有跨平台特性的服务器端程序,同时对现有的SD卡音乐播放系统进行扩展,增加UDP网络协议支持,并实现与服务器端通信报文的发送与解析工作。 系统简要的工作过程为:首先在服务器端,建立一个音频库,该音频库将与终端中存在的音频文件同步。然后,建立一周的音频播放方案指明学校中上下课的时间。服务器程序将根据选用的播放方案按照设定的时间发送广播命令报文至终端。当终端接收到命令后,将检测命令中指定的歌曲是否在SD卡中,如果存在则播放对应的歌曲。 2 服务器程序设计 为了在PC机上构建一个管理系统,选择了具有跨平台的Qt技术。Qt是一个跨平台的应用和UI框架,开发者使用C++或者UML(Unified Modeling Language)进行开发。本服务器程序的主界面如图2所示。 如图2所示,服务器程序主界面中包含了当前的系统时间、在线终端数信息、应用方案中本日的作息安排情况。系统中的两个管理按钮用于媒体管理和作息管理。在媒体管理中可以管理目前系统SD卡中的歌曲英文缩写及对应的描述信息。在作息管理中可以创建和管理播放方案。 本系统依照方案对作息进行管理,可根据需要灵活切换当前选择的播放方案。对于每个方案,可设置星期一到星期日的播放列表。 考虑到本系统中存储的信息不会太庞大,所以采用了轻量级的Sqlite数据库对方案信息和媒体信息及终端信息进行存储。

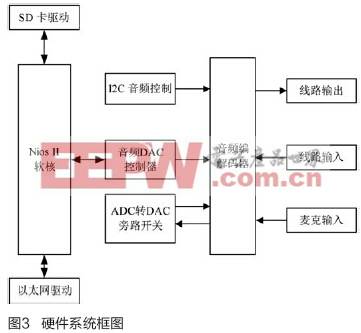

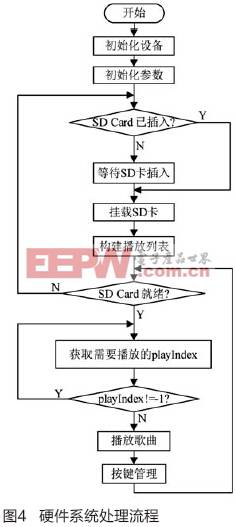

3 终端设计 通过在SoPC中查看并更改SD卡音乐播放系统的链接结构,确定了系统的硬件平台结构如图3所示,其主要改动为增加了网络模块。 如图3所示,系统通过使用Nios II软核来处理SD卡信息的读取、发送数据到音频解码模块以及和服务器进行通信。硬件系统软件的主要处理流程如图4所示。 如图4所示,当终端上电后,首先将初始化外部设备,设置初始音量等参数。当完成后,等待SD卡插入并挂载,系统创建支持的播放列表。上述初始化工作完成后,等待服务器发送播放命令并解析该播放项在播放列表中的索引值,找到后播放系统中存储的音频文件。 通常在Nios II软核上实现UDP协议有两种方式,一种为使用LwIp的方式进行处理,另一种方式则为自己实现该协议的简化版本。本系统因所需的通信量较少,为了简化软核程序采用了自己实现的方式。自己实现UDP协议主要需要注意的问题有两点:① ARP协议的实现;② UDP报文的组包和解包操作。组包流程为首先组成UDP数据包,然后组成Ip报文最终生成以太网中传输的以太网帧。这些报文格式都可以很容易地通过相关标准得到。同时,在调试系统UDP实现情况时,可通过WireShark网络监测软件对通信过程发送的信息进行监控,提高开发效率。 在UDP基本通信完成后,设定通信中服务器端命令报文的格式为:@@命令内容@;终端命令报文的格式为:@@终端序列@命令内容@。服务器程序和终端通过解析命令帧中的命令内容进行通信。 音频编解码芯片WM8731使用I2C协议进行控制,在系统工作过程中,Nios

II软核首先将检测音频DAC控制模块中的FIFO是否满,如果检测结果为非满,则Nios

II软核将通过Avalon总线读取512字节数据到FIFO中。音频DAC控制模块采用48

KHz的采样频率将数据送到音频解码模块。目前系统实现所支持的文件格式只有采用48

KHz采样频率和16bit采样深度的wav格式文件。所支持的SD卡文件格式为FAT格式。 3 总结 本文介绍了一种使用软硬件相结合实现的网络定时音频广播系统,在Altera原有项目资源的基础上通过扩展实现网络通信UDP协议、通信协议制定、服务器程序设计进行设计。从上文中可以看出,本文所实现的平台目前功能还比较单一,有待于借助网络平台的优势对系统进一步扩展,增加如视频监控、在线点播、流媒体播放等构成真正意义上的IP广播方案。 参考文献:

[1]陈琳.基于校园网的嵌入式广播系统设计[J].计算机与数字工程,2009,37(7):96-98

[2]徐源.基于 FPGA 的以太网音频广播系统的设计[D].大连海事大学,2011

[3]HAI X,ZHAO C,JIANG X.Train Station Classification for Passenger

Dedicated Line[J]. International Journal of Advancements in Computing

Technology,2012,4(15)

[4]Altera DE2

多媒体开发平台[R/OL].http://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=China&CategoryNo=60&No=31&PartNo=4

[5]LU Z,Li J,ZHANG Y.The reading/writing SD card system based on FPGA[C].Pervasive Computing Signal Processing and Applications (PCSPA), 2010 First International Conference on.IEEE,2010:419-422

[6]UEHARA T,SATO T,YAMAOKA K.The design and implementation of a music

broadcasting system via IP multicast with

user-authentication[C].Communications, Computers and signal

Processing,2003.PACRIM.2003 IEEE Pacific Rim Conference

on.IEEE,2003(2):984-987

[7]Liang Hongwei,Li Jiangai,Kan Lingling.Implementation of SD Card

Music Player Using Altera DE2-70[C].Multimedia and Signal Processing

(CMSP), 2011 International Conference on.IEEE,2011(2):150-153

下一篇:全面解析互动投影系统原理

- 利用锚定可信平台模块(TPM)的FPGA构建人形机器人安全

- 贸泽电子开售:面向工业、AI、医疗、数据中心等领域的Altera Agilex 5 FPGA与SoC

- DC到3.2GHz采样率!PXI平台+开放FPGA赋能,我们打造了一款“软件定义”的锁相放大器

- 莱迪思半导体携手EXOR International和TrustiPhi推出网络韧性参考套件

- Altera 25G Holoscan 传感器桥接器演示荣获Embedded Computing Design最佳展品奖

- 采用FPGA与双路AD9288的便携式示波器设计

- 莱迪思半导体将举办关于低功耗FPGA实现传感器附近AI推理的网络研讨会

- 发力物理 AI:Altera 以 FPGA 创新,赋能机器人及边缘场景

- 弥合传感器融合鸿沟:FPGA如何助力边缘端实时机器人应用

- FPGA在机器人领域同样是关键支撑

- 嵌入式的风向变了:2026纽伦堡嵌入式展透露这些趋势

- 高通确认不在GDC 2026发布新款骁龙G系列掌机处理器SoC

- 行业评论 从工具到平台:如何化解跨架构时代的工程开发和管理难题

- 面向嵌入式部署的神经网络优化:模型压缩深度解析

- 摩尔线程MTT S5000全面适配Qwen3.5三款新模型

- Mujoco中添加Apriltag标签并实现相机识别教程

- 英飞凌与宝马集团携手合作,基于Neue Klasse架构塑造软件定义汽车的未来

- 物理AI仿真新突破:摩尔线程与五一视界共建全栈国产化生态

- 阿里达摩院发布玄铁C950,打破全球RISC-V CPU性能纪录

- 爆火的OpenClaw! 告别云端,米尔RK3576开发板本地部署

- 边缘计算主机盒选购指南:五大核心指标解析

- Arm AGI CPU 更多细节:台积电 3nm 制程、Neoverse V3 微架构

- Arm AGI CPU 重磅发布:构筑代理式 AI 云时代的芯片基石

- Arm 拓展其计算平台矩阵,首次跨足芯片产品

- 阿里达摩院发布RISC-V CPU玄铁C950,首次原生支持千亿参数大模型

- 边缘 AI 加速的 Arm® Cortex® ‑M0+ MCU 如何为电子产品注入更强智能

- 阿里达摩院发布玄铁C950,打破全球RISC-V CPU性能纪录

- VPU中的“六边形战士”:安谋科技Arm China发布“玲珑”V560/V760 VPU IP

- 利用锚定可信平台模块(TPM)的FPGA构建人形机器人安全