RISC-V这次真的要上天了

2019-07-26 来源:EEWORLD

7月25日,阿里巴巴旗下半导体公司平头哥正式发布玄铁910(XuanTie910)RISC-V IP,着实让RISC-V火了一把。

现在,RISC-V真的要上天了。Microchip的Dorian Johnson表示,目前Microchip准备将其采用RISC-V指令集架构(ISA)的FPGA处理器应用到太空中,目前正在进行抗辐射等测试环节。

“使用新的开放式RISC-V架构,FPGA电路可以更靠近远端测量源工作。”Johnson在Elektroniikkalehti的文章中解释道。 “它可以在有效载荷源上实现自动数据收集,状态监视和负载控制,从而为卫星的CPU系统释放资源,因为它不必再负责控制远程有效载荷单元。”

“作为RISC Foundation维护的标准开放式架构,RISC-V ISA在空间技术设计中提供了许多好处。一个好处是“冻结”指令集,这意味着写入RISC-V内核的任何软件将始终可以在任何RISC-V设备上运行。使得原始代码库可以在许多不同的软件中重复使用数十年,从而使维护旧应用程序变得更加容易。合作伙伴可以创建根据客户特定要求定制RISC-V软件内核,并在需要时实现RTL共享以监控安全关键型应用程序。”

“RISC-V处理器已经在用于航空航天应用的抗辐射FPGA中进行了测试,”Johnson说道。“包含RISC-V处理器的FPGA适用于每个有效载荷单元,根据LX7730混合信号电路发送的远程测量数据进行读取,测量和决策,并将有效载荷单元的状态信息报告给或特殊的非标准化协议。“

Microchip目前概念验证阶段采用的是六传感器测试,RISC-V软核在抗强化辐射的RTG4 FPGA中运行。通过SPI总线连接到LX7730遥感控制器。

当然,并不是第一个将开放指令集带入太空的技术:TechEdSat-1 cubeat采用OpenRISC处理器,于2012年10月部署到国际空间站中,Cobham Gaisler的LEON处理器则采用基于OpenSPARC的开源架构。

LEON是一款32位RISC处理器,支持SPARC V8指令集,由欧洲航天总局旗下的Gaisler Research开发、维护,目的是摆脱欧空局对美国航天级处理器的依赖。

美国军工航天领域芯片供应商美高森美(Microsemi)在2017年时曾宣布成为首家针对RISC-V设计提供全面软件工具链和知识产权(IP)内核的可编程逻辑器件(FPGA)供应商。其RV32IM RISC-V内核适用于美高森美IGLOO2 FPGA、Smart Fusion 2系统级芯片(SoC)FPGA或抗辐射RTG4 FPGA。此后的2018年初,Microchip宣布收购美高森美,从而获得了包括军工航天,网络通信在内的多项技术。

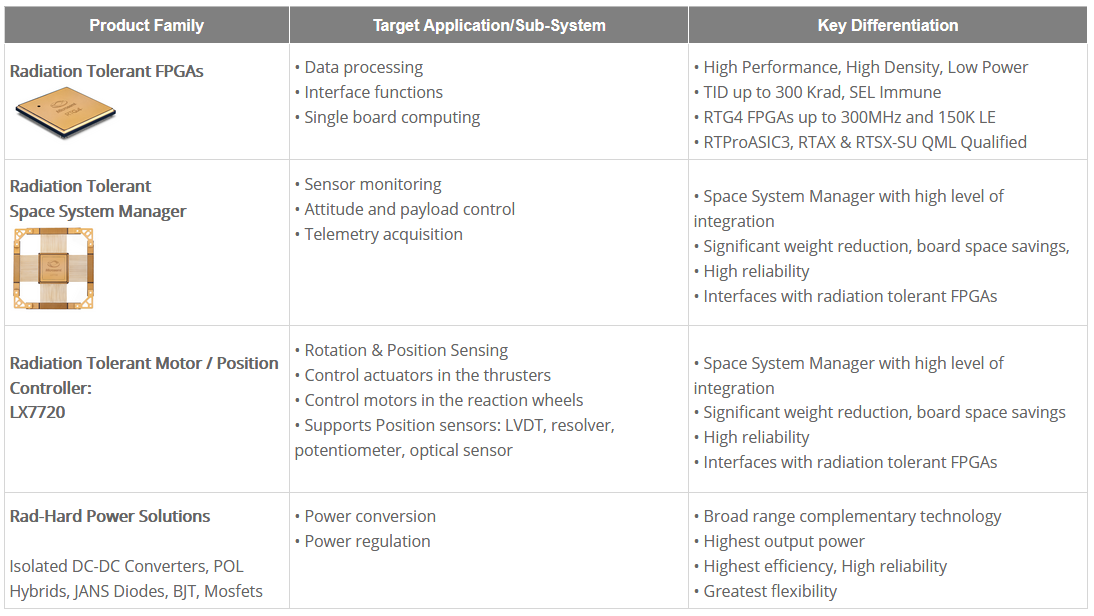

Microchip/Microsemi在卫星姿态和卫星轨道控制领域的布局

- 高通推出其首款 RISC-V 架构可编程连接模组 QCC74xM,支持 Wi-Fi 6 等协议

- SiFive CEO:RISC-V如何塑造计算的未来

- 智权半导体/SmartDV力助高速发展的中国RISC-V CPU IP厂商走上高质量发展之道

- 超2000亿美元!2029年全球SoC芯片市场猛涨,RISC-V和汽车领域机会广阔!

- IAR全面支持国科环宇AS32X系列RISC-V车规MCU

- 长城联合开发的RISC-V车规MCU成功点亮

- 基于RISC-V内核的车规MCU芯片研发及产业化丨芯车无限确认申报2024金辑奖

- 推动RISC-V CPU性能快速提升并向上打开更多的高价值市场

- 阿里达摩院玄铁推出 64 位高实时能效 RISC-V 处理器设计 R908

- 芯安全 芯动力 芯同行丨2024紫光同芯合作伙伴大会在京举行