消息称三星电子 FOPLP 先进封装研发转而聚焦 415mm × 510mm 基板

2026-03-04 来源:IT之家

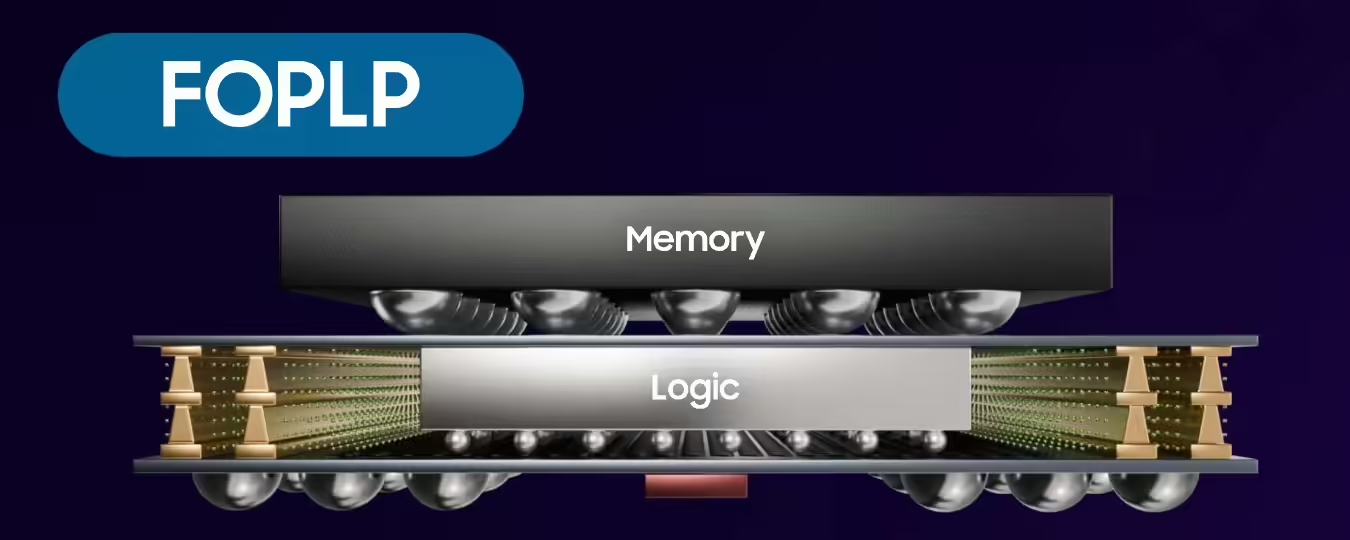

3 月 4 日消息,韩媒 the bell 当地时间 2 月 27 日报道称,三星电子已调整在下一代 FOPLP(面板级扇出封装)技术上的面板尺寸选择,将重点从现有的 600mm × 600mm 转移至 415mm × 510mm。

更大的面板尺寸固然可提升一次处理先进封装复合体数量,从而带来更高生产效率;但也意味着更大的边缘翘曲风险,会影响封装质量。该问题在三星此前将 FOPLP 用于小尺寸移动端 AP(应用处理器)时尚不明显,但对于大型 AI 芯片来说将带来严峻挑战。

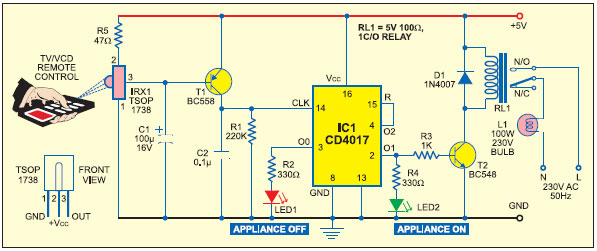

▲ 三星 FOPLP 技术示例

可以说三星电子选择聚焦 415mm × 510mm 是一种折中的选择,在保留 FOPLP 生产效率优势(IT之家注:可达 FOWLP 三倍)的同时使其更好满足未来大规模商用的需求。

FOPLP、玻璃中介层等下一代先进封装技术是台积电、三星电子、英特尔等企业当下的开发重点。现有的 CoWoS 及其类似物产能有限,是当前 AI 芯片供应链中的“卡脖子”节点之一。

相关文章

- 半年翻三倍!三星2nm良率涨至60%以上:紧追台积电

- 三星代工迎来大逆转!接连拿下NVIDIA、Tesla、AMD大单:Q4有望扭亏

- 三星电子:HBM5 与 HBM5E 将分别升级基础裸片与 DRAM 的制程

- 曝三星计划在美国得州泰勒建立第二座芯片厂,规模与第一工厂相当

- 三星回应内存短缺:预计2028年结束

- 英伟达罕见入局内存研发:联手三星共同推进铁电NAND商业化

- 三星电子:2nm 良率爬坡好于预期,泰勒晶圆厂预计年底完成首批流片

- 消息称特斯拉计划就大幅提升AI6芯片产能规模与三星电子磋商

- 是德科技与三星携手NVIDIA展示端到端AI-RAN验证工作流程

- 消息称台积电 FOPLP 先进封装技术 CoPoS 目标 2028 年底至 2029 年量产

- 半年翻三倍!三星2nm良率涨至60%以上:紧追台积电

- 倪光南:半导体行业不再是先进制程包打天下的局面

- 意法半导体与英伟达合作加快物理AI全面普及和市场增长

- 贸泽电子荣获海关AEO高级认证 ——迈向国际贸易合规与供应链安全重要里程碑

- 全国首条 8 英寸硅光芯片量产线在苏州开工建设,预计 2027 年初投产

- 不只是PCB工具:拆解 Altium Develop 背后的平台化雄心

- Agentic AI时代,RISC-V如何突围?玄铁给出了答案

- All in AI再落一子:深度解读安谋科技“玲珑”V560/V760

- 资腾亮相SEMICON China展示CMP超洁净刷轮,助力先进制程良率提升

最新频道文章