是德科技携手新思科技运用AI进行射频设计迁移

2025-08-22 来源:EEWORLD

是德科技将其电磁仿真器与新思科技的 AI 驱动射频设计迁移流程相结合,打造集成设计流程,助力从台积电 (TSMC) 的 N6RF+ 工艺技术迁移到 N4P 工艺技术。

该迁移工作流程基于晶圆代工厂的模拟设计迁移 (ADM) 方法,旨在简化无源器件和设计组件的重新设计,使其符合先进的射频工艺规则。

是德科技表示,该协作迁移工作流程充分利用了 N4P 工艺的性能提升,用于从 N6RF+ 迁移的低噪声放大器 (LNA) 设计。其组件包括带有 Synopsys ASO.ai 的 Synopsys Custom Compiler 布局环境,可快速实现模拟和射频设计迁移。其他组件包括 Synopsys PrimeSim 电路仿真器和是德科技的射频电路仿真工具 RFPro,用于器件参数化、自动数值拟合和电磁 (EM) 仿真。

该公司表示,使用人工智能加速射频电路迁移过程,并使用新思科技定制编译器 (Synopsys Custom Compiler) 和人工智能驱动的模拟设计迁移工具 ASO.ai 进行重新设计,从而确定满足性能指标的最佳设计参数。这种组合还能优化设计的 PPA(功耗、性能和面积)。

Keysight RFPro 用于对无源器件(包括电感器)进行参数化。它会自动重新创建仿真模型,并根据新的工艺规则调整布局。

Keysight 设计工程软件部门高级副总裁 Niels Faché 表示:“在遵守新的工艺设计规则的同时满足 PPA 要求是复杂射频芯片设计面临的最大挑战之一。射频电路设计人员希望利用和重复使用他们的 N6RF+ 器件和组件 IP 库来提高投资回报率 (ROI)。” 他表示,这种基于台积电 ADM 方法建模的组合意味着“无需耗时的数据交接或领域专业化,从而提高了射频电路设计人员的整体工程效率。”

在 DAC 2025 上,是德科技重点介绍了 RFPro 的首版,它为使用 Cadence Virtuoso 和 Synopsys Custom Compiler 的 RFIC 设计人员提供多物理场仿真支持。

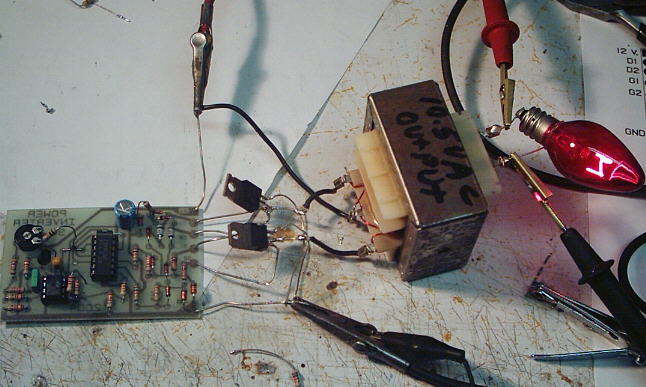

它包含 Winslow 非线性放大器稳定性分析、带误差矢量幅度 (EVM) 优化的调制信号分析,并支持用于 3D 异构集成和芯片封装的混合层次结构(如图所示)。

灵活的许可机制允许同时进行多种类型的仿真,并可在多个用户之间共享。

- 是德科技推出AI推理仿真平台,用于验证与优化AI基础设施

- 是德科技在OFC 2026上通过超以太网LLR和CBFC互操作性演示推动AI网络发展

- 是德科技推出全新 224G 测试解决方案,以支持 1.6T 光网络验证

- AI算力竞赛背后,是德科技走向台前

- 是德科技高性能误码仪:架构设计与测试原理深度剖析

- 应对AI带来的仪器行业革命,是德科技XR8示波器平台问世

- 是德科技推出Infiniium XR8示波器,加速高速数字验证与一致性测试

- 是德科技携手高通推进射频数字孪生技术,助力大规模MIMO与AI原生6G研究规模化发展

- 是德科技携手联发科技推进AI驱动的上行优化与无线接入网模型全生命周期管理

- 是德科技与三星携手NVIDIA展示端到端AI-RAN验证工作流程

- 中兴发布全球首款 Al + Wi-Fi 8 室内 CPE 及全球首款毫米波室外 5G-A CPE

- MediaTek 于 MWC 2026 展示 AI 与通信优势

- 国内首款国产InfiniBand,有什么技术关键点值得关注?

- 恩智浦MCX W72已量产,助力开发安全精准的测距应用

- 全球首个无线网络智能体落地 40万个5G基站焕新

- Gartner预测,到 2030 年,中国 80%的本地 AI 基础设施将采用本土研发的AI芯片

- Gartner发布2026年数据和分析重要预测

- MWC巴塞罗那2026:从基础到新服务,打造AI原生的6G原型

- 首款国产InfiniBand面世,实测数据告诉你性能究竟有多强悍

- 深耕智能5G,从容迈向6G:英特尔以可灵活部署 AI的网络架构,擘画产业未来

- 第三代酷睿Ultra助力商用PC大焕新,英特尔发布全新商用产品组合

- Molex 莫仕推出 145 GHz Cardinal 多端口高频同轴组件, 为 AI 和 6G 测试树立新标杆

- 拿下L3平台定点,纯固态激光雷达即将大规模交付

- 业界独家!英特尔推出革新性IBOT技术,进一步释放x86处理器性能

- 是德科技推出220GHz光波器件分析仪,支持验证新一代光收发器

- Gartner发布三大AI价值实现路径

- Intel 18A新机上市,英特尔转型跃上新台阶

- 兼顾隐私、响应与成本,基于酷睿Ultra的混合AI部署成为智能体新标配

- 别只盯着OpenClaw的Agent!它丝滑的背后,是一场硬件设计的极限挑战